- 490.50 KB

- 2022-08-30 发布

- 1、本文档由用户上传,淘文库整理发布,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,请立即联系网站客服。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细阅读内容确认后进行付费下载。

- 网站客服QQ:403074932

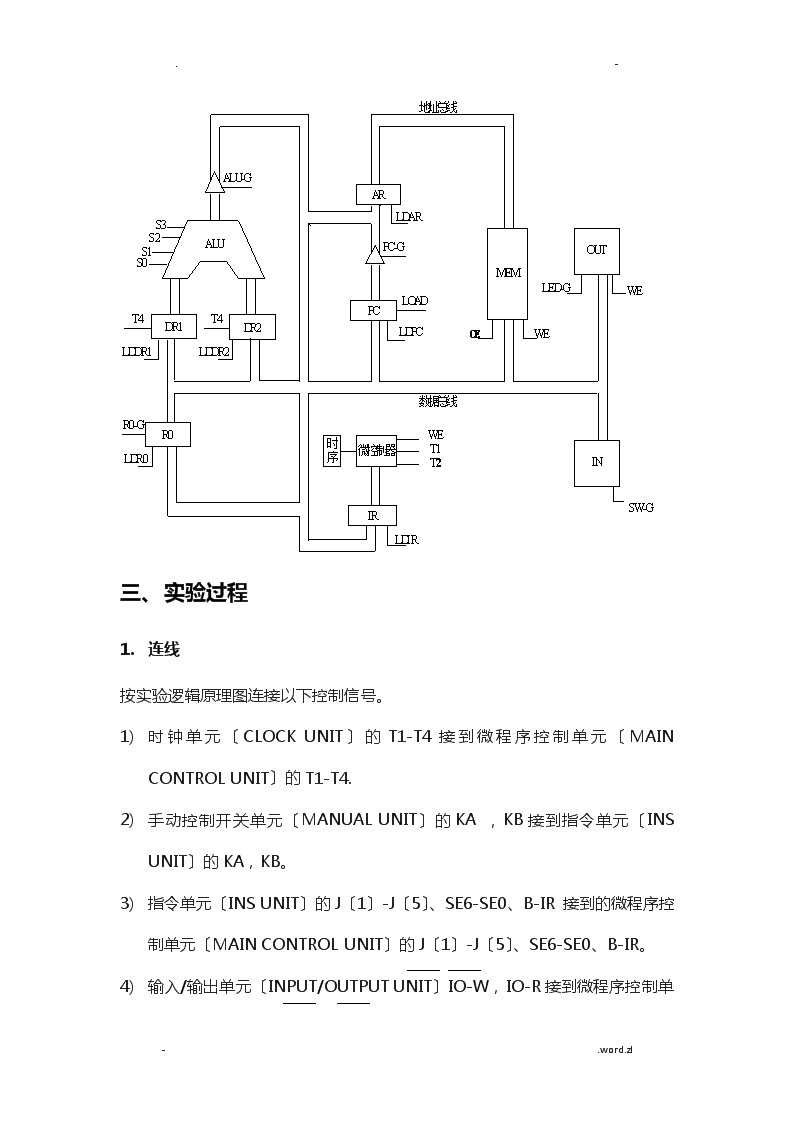

.-实验八简单模型计算机实验一、实验目的1)通过实验分析简单模型机构造,了解计算机的工作原理。2)掌握计算机微程序控制器的控制方法,掌握计算机指令执行过程二、实验原理根本整机模型数据框图如以下图,计算机数据通路的控制将由微程序控制器来完成,CPU从存中取出一条机器指令到指令执行完毕的一个指令周期全部由微指令组成的序列来完成,即一条机器指令对应一个微程序。数据的通路从程序计数器PC的地址送到主存的地址存放器,根据地址存放器的容找到相应的存储单元。存储器中的数据是指令时,那么数据是从RAM送到总线,再从总线送到IR中。存储器中的数据是需要加工的数据时,那么数据是从RAM送到总线,再动总线送到通用存放器中等待加工。数据加工过程中,两个数据是从总线上将数据分别分时压入两个暂存器中,等待运算部件的加工,在数据加工完成以后。运算结果是通过三太门送到总线上。三态门的控制时由微控制器来控制。-.word.zl\n.-图:模型机的数据通路图-.word.zl\n.-一、实验过程1.连线按实验逻辑原理图连接以下控制信号。1)时钟单元〔CLOCKUNIT〕的T1-T4接到微程序控制单元〔MAINCONTROLUNIT〕的T1-T4.2)手动控制开关单元〔MANUALUNIT〕的KA,KB接到指令单元〔INSUNIT〕的KA,KB。3)指令单元〔INSUNIT〕的J〔1〕-J〔5〕、SE6-SE0、B-IR接到的微程序控制单元〔MAINCONTROLUNIT〕的J〔1〕-J〔5〕、SE6-SE0、B-IR。4)输入/输出单元〔INPUT/OUTPUT-.word.zl\n.-UNIT〕IO-W,IO-R接到微程序控制单元〔MAINCONTROLUNIT〕的IO-W,IO-R,Ai接到地址单元〔ADDRESSUNIT〕的A0.1)主存储器单元〔MEMUNIT〕M-W、M-R接到微程序控制单元〔MAINCONTROLUNIT〕的M-W、M-R,A7-A0接到地址单元〔ADDRESSUNIT〕的A7-A0.2)地址单元〔ADDRESSUNIT〕的B-AR、B-PC、PC+1、PC-B接到微程序控制单元〔MAINCONTROLUNIT〕的B-AR、B-PC、PC+1、PC-B.3)通用存放器单元〔REGUNIT〕的B-R、R0-B接到微程序控制单元〔MAINCONTROLUNIT〕的B-DR、DR-B。4)把算术逻辑单元〔ALUUNIT〕的B-DA1、B-A2、ALU-B、Cycn、CyNCn、S3-S0、M、Ci接到微程序控制单元〔MAINCONTROLUNIT〕的B-DA1、B-A2、ALU-B、Cycn、CyNCn、S3-S0、M、Ci。1.写入、检验微代码这项操作与实验七的操作过程一样2.装入机器指令汇编程序操作1)微程序控制单元〔MAINCONTROLUNIT〕编程开关置于“RUN〞状态。2)手动控制开关单元〔MANUALUNIT〕的“STEP/RUN〞开关置于“STEP〞状态。3)手动控制开关单元〔MANUALUNIT〕的KA,KB开关置于1、0写主存储器状态。4)拨动开关从11—0—-.word.zl\n.-1,产生一个负脉冲,清零程序计数器PC、微地址存放器。1)拨动“START〞按钮一次,从微程序控制存储器的00H微地址开场执行微指令,暂停在0AH微地址处。2)此时在输入数据开关上拨入实验用机器指令汇编程序表中对应00H地址的指令码C0H,接着第二次按动“START〞按钮,暂停在0FH微地址处;第三次按动“START〞按钮,暂停在1CH微地址处;第四次按动“START〞按钮,暂停在1DH微地址处,此时机器指令汇编的第一个字节已写入存储器,程序计数器PC已加1为01H;第四次按动“START〞按钮,暂停在0AH微地址处,开场写机器指令汇编程序第二个字节。3)第六次至九次按动“START〞按钮与第二次至五次按动“START〞按钮的作用类似,当微地址为0AH时,在输入数据开关上拨入下一个机器指令汇编程序字节,程序计数器PC不断加1,反复操作第〔6〕步直至全部机器码送入主存器为止。1.检查机器指令汇编程序1)微程序控制单元〔MAINCONTROLUNIT〕编程开关置于“RUN〞状态。2)手动控制开关单元〔MANUALUNIT〕的“STRP/RUN〞开关置于“STEP〞状态。3)手动控制开关单元〔MANUALUNIT〕的KA、KB开关置于0、1写主存储器状态。4)拨动开关从1-0-1,产生一个负脉冲,清零程序计数器PC、微地址存放器。5)按动“START〞按钮一次,从微程序控制存储器00H微地址开场执行微指令,暂停在09H微指令处。-.word.zl\n.-1)第二次按动“START〞按钮,暂停在0CH微地址处,此时程序计数器PC加1为01H,指示的是下一次读主存储器的地址,当前读主存储器的地址为00H;接着第三次按动“START〞按钮,暂停在09H微地址处;第四次按动“START〞按钮,暂停在0EH微地址处。第五次按动“START〞按钮,暂停在09H微地址处,此时输出显示灯上显示主存储器00H单元中的数据。2)第六至九次按动“START〞按钮的作用与第二至五次按动“START〞按钮的作用类似,在0CH微地址处,程序计数器PC加1,在09H微地址处显示主存储器相对应单元中的数据,反复操作第〔6〕步直至全部机器码读出检查完为止。3)如果主存储器中数据与表2-26中数据不符,那么回到第三步装入机器指令汇编程序的操作过程,重新向主存储器写入正确数据。1.单步运行机器指令汇编程序1)微程序控制单元〔MAINCONTROLUNIT〕编程开关置于“RUN〞状态。2)手动控制开关单元〔MANUALUNIT〕的“STRP/RUN〞开关置于“STEP〞状态。3)手动控制开关单元〔MANUALUNIT〕的KA、KB开关置于1、1或0、0运行机器码状态。4)拨动开关从1-0-1,产生一个负脉冲,清零程序计数器PC、微地址存放器。5)按动“START〞按钮一次,从微程序控制存储器的00H微地址开场执行微指令,暂停在08H或0BH微地址处;第二次按动“START〞按钮,暂停在01H微地址处,开场执行机器指令的公共操作。6)第三次按动“START〞按钮,暂停在02H微地址处;第四次按动“-.word.zl\n.-START〞按钮,暂停在03H微地址处;接着第五次按动“START〞按钮,暂停在10H微地址处,准备各条机器指令的散转。1)接下来微地址随着主存储器中机器指令汇编程序指令的不同而作不同的变化,实验者可根据表2-26和表2-15中的容观察各部件的动作变化。1.连续运行机器指令汇编程序1)微程序控制单元编程开关置于“RUN〞状态。2)手动控制开关单元的“STEP/RUN〞开关置于“RUN〞状态。3)手动控制开关单元的KA、KB开关置于1、1或0、0运行机器码状态。4)拨动开关从1-0-1,产生一个负脉冲,清零程序计数器PC、微地址存放器。5)按动“START〞按钮一次,模型计算机将自动执行表2-26中的机器指令汇编程序,程序功能是对输入数据开关上的数据进展连续加操作,假设在输入数据开关上拨01H,那么进展连续加“1〞操作;假设拨03H,那么进展连续加“3〞操作。一、微指令运行步骤机器指令写入控制台指令机器指令读出机器指令执行取指译码机器指令执行执行-.word.zl\n.-访存写回-.word.zl\n.-一、结果与总结1)记录实验过程中的情况和原始数据。2)参照算术加法指令的微程序操作过程,能否自己设计一条无借位算术减法指令的微程序操作代码,以扩大模拟计算机的功能。3)记录每条机器指令完毕时的模拟模型计算机各指示灯上的信息,用16进制形式填入表2-27中,并说明这些信息的意义。4)结合上面的问题总结出总线的特性和使用方法,以及解决问题的方法和过程,把观察到的现象和对书本上原理的理解写入实验报告。表2-27实验八结果记录机器状态输入指示灯总线指示灯微地址指示灯微指令码指示灯输出指示灯指示灯信息含义初始状态01FF0001C00894将执行00地址中的指令01C008H控制台指令完毕时01FF01DC400294执行完后地址跳转至01HIN完毕时01010194输入01H中的数据ADD完毕时01950194与输入数相加STA完毕时01950194将结果送01HOUT完毕时01950195-.word.zl\n.-将01H数据输出JMP完毕时01000195跳转至00H一、附录实验箱介绍PC微机逻辑分析及监测〔单片机〕RS运算器存放器报警输入/输出中断主存储器总线微程序控制器指令地址时钟手动控制开关实验仪根本组成框图1.简单模型计算机构架简单模型计算机逻辑构造如图1所示,构成简单模型计算机的实验部件以总线为根本连接通道,主要有以下7个:1)算术逻辑运算部件ALUUNIT进展算术逻辑运算操作。-.word.zl\n.-1)存储器部件MEMUNIT,存储模型计算机汇编语言程序和操作数据。2)地址存放器部件ADDRESSUNIT,包含两局部电路,地址存放器AR:接收存储器程序中的指令地址和指令中的数据地址;指令地址计数器PC:用于指示程序中的指令地址并通过地址缓冲器送往地址存放器AR。3)指令存放器部件INSUNIT,存放器当前正在执行的机器指令,此指令的指令码通过指令译码器向微程序控制器指示相应的微程序入口地址;此指令的地址码指示的操作数地址,送往地址存放器AR。4)输入/输出部件INPUT/OUTPUT,操作数据的输入与输出显示。5)通用存放器部件REGUNIT,暂存运算的中间数据。6)微程序控制器部件MAINCONTROLUNIT,控制各部件完成指令的功能。-.word.zl\n.-图1-简单模型计算机逻辑构造图1.总线构造总线是多个系统部件之间进展数据传送的公共通路,是构成计算机系统的骨架。借助总线连接,计算机在系统各部件之间实现传送地址、数据和控制信息的操作。因此,所谓总线就是指能为多个功能部件效劳的一组公用信息线。总线传输实验框图如以下图所示,它将几种不同的设备挂至总线上,有存储器、输入设备、输出设备、存放器。这些设备都需要有三态输出控制,按照传输要求恰当有序的控制它们,就可实现总线信息传输。2.运算器ALU运算器ALU由一片ispLSI1024〔U47〕组成,在选择端S2、S1、S0控制下,对数据A和B进展加、减、与、直通、乘五种运算,功能如下:运算器功能表选择操作S2S1S0000A&B001A&A(直通)010A+B011A-B100A〔低4位〕×B〔低4位〕-.word.zl\n.-进位C只在加法运算和减法运算时产生。加运算中,C表示进位;减运算中,C代表借位。加、减运算产生的进位〔借位〕在T4的上升沿送入C存放器保存。与、乘、直通操作不影响进位C的状态,即进位C保持不变。当ALU_BUS=1时,运算结果送往数据总线DBUS。加、减运算产生的进位〔借位〕C与控制台的C指示灯相连。1.地址存放器地址存放器AR1〔U37〕和AR2〔U27、U28〕提供双端口存储器的地址。AR1是一片GAL22V10,具有加1功能,提供双端口存储器左端口的地址。AR1从数据总线DBUS接收数据。AR1的控制信号是LDAR1和AR1_INC。当AR1_INC=1时,在T4的上升沿,AR1的值加1;当LDAR1=1时,在T4的上升沿,将数据总线DBUS的数据打入地址存放器AR1。AR2由2片74HC298组成,有两个数据输入端,一个来自程序计数器PC,另一个来自数据总线DBUS。AR2的控制信号是LDAR2和M3。M3选择数据来源,当M3=1时,选中数据总线DBUS;当M3=0时,选中程序计数器PC。LDAR2控制何时接收地址,当LDAR2=1时,在T2的下降沿将选中的数据源上的数据打入AR2。2.指令存放器-.word.zl\n.-指令存放器IR是一片74HC374〔U20〕。它的数据端从双端口存储器接收数据〔指令〕。当LDIR=1时,在T4的上升沿将来自双端口存储器的指令打入指令存放器IR保存。指令的操作码局部送往控制器译码,产生各种所需的控制信号。大多数情况下,指令的操作数局部应连到存放器堆〔用户自己连接〕,选择参与运算的存放器。在某些情况下〔条件转移指令时〕,指令的操作数局部也参与新的PC的计算。本实验系统设计了12条根本的机器指令,均为单字长〔8位〕指令。指令功能及格式如表2所示。表2中的X代表随意值;RS1、RS0指的是存放器堆的B端口选择信号RS1、RS0;RD1、RD0指的是存放器堆的A端口选择信号RD1、RD0,不过由于运算结果需写回,因此它也同时指WR1、WR0,用户需将它们对应连接。另一点需说明的是,为了简化运算,指令JCD中的D是一个4位的正数,用D3D2D1D0表示。机器指令格式名称助记符功能指令格式R7R6R5R4R3R2R1R0加法ADDRd,RsRd+Rs®Rd0000RS1RS0RD1RD0减法SUBRd,RsRd-Rs®Rd0001RS1RS0RD1RD0乘法MULRd,RsRd*Rs®Rd0010RS1RS0RD1RD0逻辑与ANDRd,RsRd&Rs®Rd0011RS1RS0RD1RD0存数STARd,[Rs]Rd®[Rs]0100RS1RS0RD1RD0取数LDARd,[Rs][Rs]®Rd0101RS1RS0RD1RD0无条件转移JMP[Rs][Rs]®PC1000RS1RS0××条件转移JCD假设C=1,PC+D®PC1001D3D2D1D0-.word.zl\n.-假设C=0,PC+1®PC停机STP暂停运行0110××××中断返回IRET返回断点1010××××开中断INTS允许中断1011××××关中断INTC制止中断1100××××1.时序发生器时序发生器产生计算机模型所需的时序。时序电路由一个1MHz晶体震荡器、2片GAL22V10〔U6和U7〕组成,位于控制存储器的右边。根据本机设计,执行一条微指令需要4个节拍脉冲T1、T2、T3、T4,执行一条指令通常需要取指、送操作数、运算、写结果四个节拍电位W1、W2、W3、W4,因此本机的根本时序如下:教育之通病是教用脑的人不用手,不教用手的人用脑,所以一无所能。教育革命的对策是手脑联盟,结果是手与脑的力量都可以大到不可思议。-.word.zl