- 1.51 MB

- 2022-06-14 发布

- 1、本文档由用户上传,淘文库整理发布,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,请立即联系网站客服。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细阅读内容确认后进行付费下载。

- 网站客服QQ:403074932

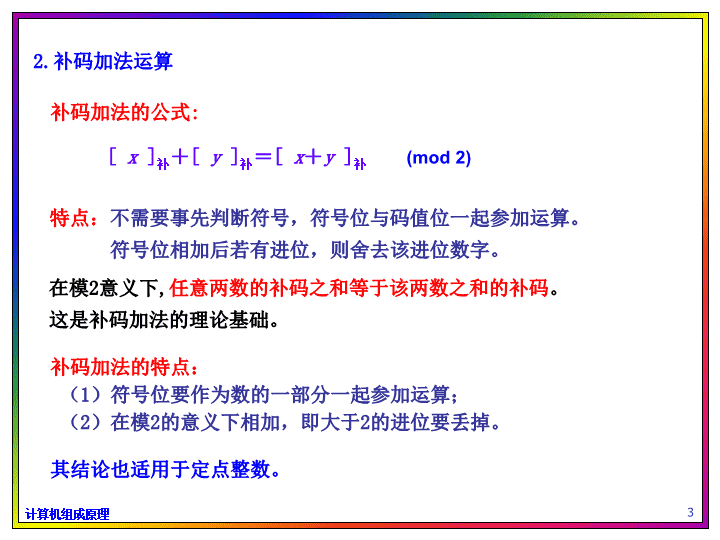

计算机组成原理Wednesday,September08,2021补码加减法运算\n加法规则:先判符号位,若相同,绝对值相加,结果符号不变;若不同,则作减法,|大|-|小|,结果符号与|大|相同。减法规则:两个原码表示的数相减,首先将减数符号取反,然后将被减数与符号取反后的减数按原码加法进行运算。补码加减法运算1.原码加/减法运算\n补码加法的公式:[x]补+[y]补=[x+y]补(mod2)在模2意义下,任意两数的补码之和等于该两数之和的补码。这是补码加法的理论基础。2.补码加法运算特点:不需要事先判断符号,符号位与码值位一起参加运算。符号位相加后若有进位,则舍去该进位数字。补码加法的特点:(1)符号位要作为数的一部分一起参加运算;(2)在模2的意义下相加,即大于2的进位要丢掉。其结论也适用于定点整数。\n例:x=0.1001,y=0.0101,求x+y。解:[x]补=0.1001,[y]补=0.0101[x]补0.1001+[y]补0.0101[x+y]补0.1110所以x+y=+0.1110例:x=+0.1011,y=-0.0101,求x+y。所以x+y=0.0110解:[x]补=0.1011,[y]补=1.1011[x]补0.1011+[y]补1.1011[x+y]补10.0110\n3.补码减法减法运算化为加法完成。关键是求[-Y]补补码减法运算的公式:[x-y]补=[x]补-[y]补=[x]补+[-y]补公式证明:只要证明[–y]补=–[y]补,上式即得证。∵[x+y]补=[x]补+[y]补(mod2)令y=-x∴[0]补=[x]补+[-x]补故[-x]补=-[x]补(mod2)证明:两数差的补码等于两数补码之差\n例:x=+0.1101,y=+0.0110,求x-y。解:[x]补=0.1101[y]补=0.0110[-y]补=1.1010∴x-y=+0.0111解:[x]补=1.0011[y]补=1.1010[-y]补=0.0110[x]补1.0011+[-y]补0.0110[x-y]补1.1001例:x=-0.1101,y=-0.0110,求x-y=?∴x-y=-0.0111[x]补0.1101+[-y]补1.1010[x-y]补10.0111\n溢出及与检测方法在定点小数机器中,数的表示范围为|x|<1。在运算过程中如出现大于1的现象,称为“溢出”。机器定点小数表示上溢下溢1.概念发生溢出的原因,是因为运算结果超出编码所能表示的数字大小。两个正数相加:结果大于机器所能表示的最大正数,称为上溢;两个负数相加:结果小于机器所能表示的最小负数,称为下溢。\n解:[x]补=0.1011[y]补=0.1001[x]补0.1011+[y]补0.1001[x+y]补1.0100例:x=+0.1011,y=+0.1001,求x+y。例:x=-0.1101,y=-0.1011,求x+y。解:[x]补=1.0011[y]补=1.0101[x]补1.0011+[y]补1.0101[x+y]补0.1000两个正数相加的结果成为负数,这显然是错误的。两个负数相加的结果成为正数,这同样是错误的。0.10101+0.010000.111011.10101+1.110001.011011正常结果正常结果\n2.溢出的检测方法[x]补0.1011+[y]补0.1001[x+y]补1.0100[x]补1.0011+[y]补1.0101[x+y]补0.1000溢出逻辑表达式为:V=S1S2Sc+S1S2Sc(1)单符号位检测方法1FAVz0y0x0判断电路判断电路设两数符号位分别为S1、S2和数符号位SC\n(2)单符号位检测方法20.10101+0.010000.111010.10101+0.11000.0110111.10101+1.110001.0110111.00101+1.11000.1110101符号位进位Cf,最高位进位CnCf=0,Cn=0Cf=1,Cn=1Cf=0,Cn=1Cf=1,Cn=0\nFAFAz1z0Vc1c0y1x1y0x0V=C1⊕Co判断电路从上面例中看到:当最高有效位有进位而符号位无进位时,产生上溢;当最高有效位无进位而符号位有进位时,产生下溢。(简单地说是正数相加为负数或负数相加为正数则产生溢出)故溢出逻辑表达式为:V=Cf⊕Co其中Cf为符号位产生的进位,Co为最高有效位产生的进位。此逻辑表达式也可用异或门实现。\n一个符号位只能表示正、负两种情况,当产生溢出时,符号位的含义就会发生混乱。如果将符号位扩充为两位(Sf1、Sf2),其所能表示的信息量将随之扩大,既能判别是否溢出,又能指出结果的符号。(3)双符号位法双符号位法也称为“变形补码”或“模4补码”。定点小数变形补码定义:[x]补=x0x<14+x-1x<0(mod4)字长n+2定点整数,变形补码定义:(mod2)x0x<22+x-2x<0[x]补=nnn+2n+2\n•任何小于1的正数:两个符号位都是“0”,即00.x1x2...xn;•任何大于-1的负数:两个符号位都是“1”,即11.x1x2…xn两数变形补码之和等于两数和的变形补码,要求:•两个符号位都看做数码一样参加运算;•两数进行以4为模的加法,即最高符号位上产生的进位要丢掉。模4补码加法公式:[x]补+[y]补=[x+y]补(mod4)采用变形补码后数的表示:\n双符号数溢出检测00.10101+00.0100000.1110100.10101+00.11000.011010111.10101+11.1100011.01101111.00101+11.11000.11101101非正常符号位,溢出符号位进位舍去,正常结果正常结果非正常符号位,溢出\nSf1Sf2=00结果为正数,无溢出01结果正溢10结果负溢11结果为负数,无溢出即:结果的两个符号位的代码不一致时,表示溢出;两个符号位的代码一致时,表示没有溢出。不管溢出与否,最高符号位永远表示结果的正确符号。溢出逻辑表达式为:V=Sf1⊕Sf2式中:Sf1和Sf2分别为最高符号位和第二符号位,此逻辑表达式可用异或门实现。双符号位的含义如下:FAFAVz1c0c1z0x1y1y0x0\n解:[x]补=00.1100[y]补=00.1000[x]补00.1100+[y]补00.100001.0100符号位出现“01”,表示已溢出,正溢。即结果大于+1例x=+0.1100,y=+0.1000,求x+y。解:[x]补=11.0100[y]补=11.1000[x]补11.0100+[y]补11.100010.1100符号位出现“10”,表示已溢出,负溢出。即结果小于-1例x=-0.1100,y=-0.1000,求x+y。\n基本的二进制加法/减法器一位全加器真值表输入输出AiBiCiSiCi+10000000110010100110110010101011100111111逻辑方程1.一位全加器FASiAiBiCiCi+1一位全加器\n逻辑方程FACi+1CiSiAiBi逻辑符号Ci+1≥1&CiAiBiSi=1=1&\n2.n位的行波进位加减器n个1位的全加器(FA)可级联成一个n位的行波进位加减器。\nT被定义为相应于单级逻辑电路的单位门延迟。T通常采用一个“与非”门或一个“或非”门的时间延迟来作为度量单位。3.n位的行波进位加法器的问题3TXNOR异或非3TXOT异或2TOR或2TAND与TNOT非TNOR或非TNAND与非时间延迟逻辑符号(正逻辑)门的功能门的名称典型门电路的逻辑符号和延迟时间接线逻辑(与或非)AOIT+TRC\n(1)对一位全加器(FA)来说,Si的时间延迟为6T(每级异或门延迟3T);Ci+1的时间延迟为5T。Ci+1≥1&CiAiBiSi=1=1&\n(2)n位行波进位加法器的延迟时间ta为:•9T为最低位上的两极“异或”门再加上溢出“异或”门的总时间;•2T为每级进位链的延迟时间。ta=n·2T+9T=(2n+9)T考虑溢出检测时,有:当不考虑溢出检测时,有:ta=(n-1)·2T+9Tta为在加法器的输入端输入加数和被加数后,在最坏的情况下加法器输出端得到稳定的求和输出所需要的最长时间。ta越小越好。由一位全加器(FA)构成的行波进位加法器:缺点:(1)串行进位,它的运算时间长;(2)只能完成加法和减法两种操作而不能完成逻辑操作。能否提前产生各位的进位输入?使得各位的加法运算能并行起来,即可提高多位加法器运算速度\n并行加法器进位链Si=Ai⊕Bi⊕Ci-1Ci=Ci-1(Ai⊕Bi)+AiBiGi=AiBiPi=Ai⊕BiGi进位生成函数GeneratePi进位传递函数PropagateCi=Gi+PiCi-1Cn=AnBn+(An⊕Bn)Cn-1=Gn+PnCn-1Cn-1=An-1Bn-1+(An-1⊕Bn-1)Cn-2=Gn-1+Pn-1Cn-2……C1=A1B1+(A1⊕B1)C0=G1+P1C0高位的运算依赖于低位运算的进位输入计算不能并行能否提前得到当前位的进位输入??\n并行加法器进位链C1=A1B1+(A1⊕B1)C0=G1+P1C0C2=A2B2+(A2⊕B2)C1=G2+P2C1=G2+P2(G1+P1C0)=G2+P2G1+P2P1C0……C3=A3B3+(A3⊕B3)C2=G3+P3C2=G3+P3(G2+P2G1+P2P1C0)=G3+P3G2+P3P2G1+P3P2P1C0Cn-1=Gn-1+Pn-1Gn-2+Pn-1Pn-2Gn-3…+PnPn-1…P1C0Cn=Gn+PnGn-1+PnPn-1Gn-2+PnPn-1Pn-2Gn-3…+PnPn-1Pn-2…P1C0位数越长,进位链电路复杂度越高通常按照4位一组进行分组运算\nA1B1G1P1=1&A2B2G2P2=1&A3B3G3P3=1&A4B4G4P4=1&与门异或门电路&&&G4P4G3P3G2P2G1P1c4c3c2c1≥1≥1&&&≥1&&&&≥1先行进位电路\n四位快速加法器与门异或门电路G4P4G3P3G2P2G1P1X4Y4X3Y3X2Y2X1Y1=1=1=1=1C0先行进位电路G4P4G3P3G2P2G1P1C4C3C2C1A4B4A3B3A2B2A1B1S4S3S2S1C4\n4位快速加法器C4C016位加法器快速加法器C16快速加法器C12快速加法器C8快速加法器C4C0组内先行进位组间串行进位可否组间并行?\n成组进位C4=G4+P4G3+P4P3G2+P4P3P2G1+P4P3P2P1C0G4*=G4+P4G3+P4P3G2+P4P3P2G1成组进位发生输出P4*=P4P3P2P1成组进位传递函数C4=G4*+P4*C0C1=G1+P1C0比较原相邻位进位公式C4=G4*+P4*C0C8=G8*+P8*(G4*+P4*C4)=G8*+P8*G4*+P8*P4*C0C16=G16*+P16*G12*+P16*P12*G8*+P16*P12*P8*G4*+P16*P12*P8*P4*C0用4组P*G*作输入,即可复用原先行进位电路产生组间先行进位信号\n先行进位电路74182输入:P4G4P3G3P2G2P1G1C0输出:先行进位输出C4C3C2C1成组进位传送输出P*成组进位发生输出G*Cn=Gn+PnGn-1+PnPn-1Gn-2+PnPn-1Pn-2Gn-3…+PnPn-1…P1C0Gi=XiYiPi=Xi⊕Yi先行进位电路74182P4G4P3G3P2G2P1G1C0C4C3C2C1P*G*\n先行进位的多功能算术/逻辑运算单元ALU74181Cn+4S3S2S1S0A3A2A1A0B3B2B1B0CnMA=BPGSN741814位ALUF3F2F1F018202211921232781415171311109163456C0\n\n16位组内先行进位,组间先行进位ALU74181A16B16A15B15A14B14A13B13C12P16G16ALU74181A12B12A11B11A10B10A9B9C8P12G12ALU74181A8B8A7B7A6B6A5B5C4P8G8ALU74181A4B4A3B3A2B2A1B1C0P4G4P*G*P4G4C3P3G3C2P2G2C1P1G1CLA(74182)C0C4\nC0P*G*C3C2C1CLA(74182)C4PGCoutC0PGCoutC0C0P*G*C3C2C1CLA(74182)CoutC0PGCoutC0PGCoutC0PGCoutC0PGCoutC0PGCoutC032位先行进位系统\n64位先行进位系统C3C2C1PGPGC0P*G*CLA(74182)PGPGC0C3C2C1PGPGP*G*CLA(74182)PGPGC0C3C2C1PGP*G*CLA(74182)PGPGPGP*G*C3C2C1PGC0CLA(74182)PGPGPGP4G4C3P3G3C2P2G2C1P1G1CLA(74182)C0\n先行进位电路时间延迟分析Cn=Gn+PnGn-1+PnPn-1Gn-2…+PnPn-1…P1C0假设所有门电路均按照2输入Gn需要1个门电路延迟PnGn-1需要2个门电路延迟PnPn-1Gn-2需要3个门电路延迟PnPn-1…P1C0需要n+1个门电路延迟考虑并发,时间延迟级别[log2(2n+1)]+1\n十进制加法器十进制加法器可由BCD码(二-十进制码)来设计,它可以在二进制加法器的基础上加上适当的“校正”逻辑来实现。70111+6+0110131101(=D)+011010011(=13)30011+5+010181000X+Y+C<10不调整X+Y+C>10调整和数(4位)有进位调整2800101000+9+000010013700110001(=31)+0000011000110111(=37)故:1.和为10~15时,加6校正;2.和数有进位时,加6校正。\n一位BCD码行波式进位加法器一般结构:1101010111100110111101111n位BCD码行波式进位加法器一般结构: