- 1.21 MB

- 2022-06-14 发布

- 1、本文档由用户上传,淘文库整理发布,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,请立即联系网站客服。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细阅读内容确认后进行付费下载。

- 网站客服QQ:403074932

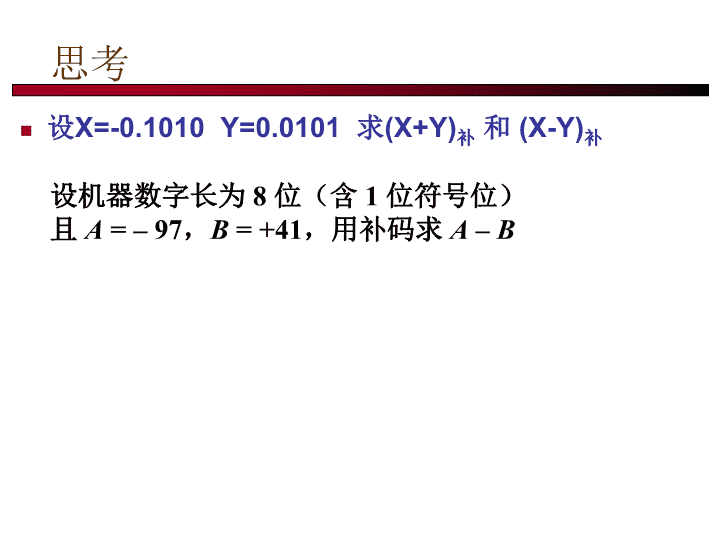

思考设X=-0.1010Y=0.0101求(X+Y)补和(X-Y)补设机器数字长为8位(含1位符号位)且A=–97,B=+41,用补码求A–B\n思考定点整数、小数有原码、补码表示形式,手工在纸上怎么加减?举例分析(两正数相加、两负数相加、正负两个数相加)。[x]原+[y]原=?[x+y]原;[x]原+[-y]原=?[x-y]原[x]补+[y]补=?[x+y]补;[x]补+[-y]补=?[x-y]补计算机中表示数据的寄存寄或存储单元长度固定,如果运行结果超过这个长度会产生什么结果?什么情况下会发生超出表示范围的现象?这个结果能否被利用?试从计算机的角度来判断运算结果什么时候出错了?\n定点数加减运算\n课程结构计算机系统统计硬件运算器数据表示数据数据定点原码反码补码移码浮点一般表示规格化IEEE754非数值数据字符汉字BCD码校验码奇偶校验海明校验循环冗余校验运算方法定点数补码加减乘除浮点数加减乘除规格化溢出判断运算器一般运算快速运算典型ALU存储器控制器总线输入输出软硬件接口软件\n主要内容定点补码加减法溢出检测基本加法器\n解:[A]补[B]补[A]补+[B]补+=0.1011=1.1011=10.0110=[A+B]补验证例设A=0.1011,B=–0.0101求[A+B]补0.1011–0.01010.0110∴A+B=0.0110[A]补[B]补[A]补+[B]补+=1,0111=1,1011=11,0010=[A+B]补验证–1001–1110–0101+例设A=–9,B=–5求[A+B]补解:∴A+B=–1110\n①补码加法的运算公式为:[x+y]补=[x]补+[y]补②补码减法的运算公式为:[x-y]补=[x]补+[-y]补③加减法运算规则:·参加运算的数都用补码表示。·数据的符号与数据一样参加运算。·求差时将减数求补,用求和代替求差。·运算结果为补码。如果符号位为0,表明运算结果为正;如果符号位为1,则表明运算结果为负。·符号位的进位为模值,应该丢掉。定点补码加减法\n①补码加法的运算公式为:[x+y]补=[x]补+[y]补证明:下面以模为2定义的补码为例,分几种情况来证明这个公式。(1)x>0,y>0,则x+y>0由于参加运算的数都为正数,故运算结果也一定为正数。又由于正数的补码与真值有相同的表示形式,即[x]补=x[y]补=y所以[x]补+[y]补=x+y=[x+y]补(2)x>0,y<0,则x+y>0或x+y<0当参加运算的数一个为正数,一个为负数时,则运算结果有正、负两种可能。根据补码定义有:[x]补=x[y]补=2+y所以[x]补+[y]补=2+(x+y)当x+y>0时,2+(x+y)>2,2为符号位进位,即模丢掉。又因为(x+y)>0,所以[x]补+[y]补=x+y=[x+y]补当x+y<0时,2+(x+y)<2,又因为(x+y)<0,所以[x]补+[y]补=2+x+y=[x+y]补这里应将(x+y)看成一个整体。定点补码加减法\n(3)x<0,y>0,则x+y>0或x+y<0这种情况和第②种情况类似,即把x与y的位置对调即可得证。(4)x<0,y<0,则x+y<0由于参加运算的数都为负数,故运算结果也一定为负数。又由于负数的补码为:[x]补=2+x[y]补=2+y所以[x]补+[y]补=2+(2+x+y)由于x+y为负数,其绝对值又小于1,那么(2+x+y)就一定是小于2而大于1的数,所以上式等号右边的2必然丢掉,又因为x+y<0,所以[x]补+[y]补=(2+x+y)=2+(x+y)=[x+y]补至此证明了在模为2的定义下,任意两个数的补码之和等于该两个数之和的补码。这是补码加法的理论基础,其结论也适用于定点整数。定点补码加减法\n②补码减法的运算公式为:[x]补-[y]补=[x]补+[-y]补证明:因为[x]补+[y]补=[x+y]补令x=-y代入,则有[-y]补+[y]补=[-y+y]补=[0]补=0所以-[y]补=[-y]补所以:[x]补-[y]补=[x]补+(-[y]补)=[x]补+[-y]补定点补码加减法\n不难发现,只要能通过[y]补求得[-y]补,就可以将补码减法运算化为补码加法运算。已知[y]补,求[-y]补的法规是:对[y]补各位(包括符号位)取反、末位加1,就可以得到[-y]补。例如:已知[y]补=1.1010,则[-y]补=0.0110;又如:已知[y]补=0.1110,则[-y]补=1.0010;定点补码加减法\n\n(1)设X=-0.1010Y=0.0101求(X+Y)补和(X-Y)补解:(X)补=1.0110(Y)补=0.0101(-Y)补=1.1011(X)补1.0110(X)补1.0110+(Y)补0.0101+(-Y)补1.1011(X+Y)补1.1011(X-Y)补1.0001X+Y=-0.0101X-Y=-0.1111加减法运算示例\n(2)设X=-0.1011Y=-0.0101求(X+Y)补和(X-Y)补解:(X)补=1.0101(Y)补=1.1011(-Y)补=0.0101(X)补1.0101(X)补1.0101+(Y)补1.1011+(-Y)补0.0101(X+Y)补1.0000(X-Y)补1.1010X+Y=-1X-Y=-0.0110加减法运算示例\n例练习1设x=y=,用补码求x+y9161116x+y=–0.1100=1216–练习2设机器数字长为8位(含1位符号位)且A=–97,B=+41,用补码求A–BA–B=+1110110=+118错错\n溢出判断由于机器码的位数通常是给定的(如16位字长,32位字长),因此,数的表示范围是有限的,若两数进行加减运算的结果超出给定的取值范围,就会产生溢出。溢出是指运算结果超过了数的表示范围。两个符号相同的数相加,才可能产生溢出;两个符号相异的数相加,不可能产生溢出。例,X=+0.1011,Y=+0.1001,X+Y=?[X]补0.1011+[Y]补0.10011.0100此时,两个正数相加的结果成为负数,显然是错误的。\n溢出判断又如,X=-0.1101,Y=-0.1011,X+Y=?[X]补1.0011+[Y]补1.01010.1000两个负数相加的结果成为正数,这同样是错误的。为判断溢出是否产生,可以采用三种检测方法。\n溢出判断1、单符号位操作检测方法:当运算结果的符号位与操作数的符号位不一致时,表示溢出;当加数和被加数符号位不同时,相加的结果绝对不会溢出。例,X=+0.1001,Y=+0.1110,用模2补码运算判断x+y是否溢出?[X]补0.1001+[Y]补0.11101.0111运算结果产生溢出。XfYfSfV00111101其它0\n溢出判断2、进位检测法CfC0

00正确(正数)01上溢10下溢11正确(负数)V=Cf⊕C0,其中Cf为符号位产生的进位,C0为最高有效位产生的进位。看高位的进位输入与其进位输出是否一致\n从真值表可判断当两个单符号位补码进行加减运算时,若最高数值位向符号位的进位值C0与符号位产生的进位输出值Cf相同时,则没有溢出发生。如果两个进位值不同,则有溢出发生。溢出表达式:V=Cf⊕C0。设xf和yf表示两个相加数的符号,C0表示高位的进位信号,Cf表示符号位的进位信号,S表示结果的符号,V为溢出信号\n例,X=+0.1011,Y=+0.1101[X]补0.1011+[Y]补0.11011.1000若最高数值位向符号位的进位为1,符号位产生的进位为0,表示有溢出。又如,X=-0.1011,Y=-0.1100[X]补1.0101+[Y]补1.01000.1001若最高数值位向符号位的进位为0,符号位产生的进位为1,表示有溢出。溢出判断\n3、变形补码检测法(双符号位)方法:每个操作数在运算时都采用两个符号位,正数用00表示,负数用11表示,两个符号位与码值一起参加运算;若运算结果的两个符号位的代码不一致时表示溢出,两个符号位代码一致时,没有溢出。设左边第一位为第一符号位Sf1,相邻的为第二符号位Sf2,则溢出逻辑表达式:V=Sf1⊕Sf2若V=0无溢出;V=1有溢出。溢出判断\n数据截断用8位原码表示5/2560.000001015/128+1/256+1/256=?1/256+1/256+5/128=?开放问题:某个截断错误出现在一个关键时刻,引起了的损失和人身伤亡。如果有人需要对此负责,那么是谁?硬件设计者?软件设计者?编写那段程序的程序员?决定使用这个软件的人?\n基本的加法器基本的加法和减法器半加器Hi=Ai⊕Bi不考虑进位全加器

考虑低位进位Ci-1和向高位的进位Ci\n一位全加器真值表输入输出AiBiCiSiCi+10000000110010100110110010101011100111111基本的加法器\n基本的加法器-FA逻辑电路和框图FA(全加器)逻辑电路图FA框图\n图 行波进位的补码加法/加法器基本的加法器-n位行波进位加法器\n基本的加法器-n位行波进位加法器B0A0MB1A1Bn-2An-2Bn-1An-1溢出S0S1Sn-2Sn-1一个“与”门或者一个“或”门的时间延迟为一个T,异或门为3T0时刻3T时刻4T时刻6T时刻6T+2T时刻9T时刻6T+4T时刻6T+2nT时刻6T+2(n-1)T时刻11T时刻6T+2(n-1)T+3T时刻6T+2nT+3T时刻C0C2Cn-1C1Cn\n基本的加法器-实现加法的逻辑图①实现加法时应提供以下控制信号:A→ALU,B→ALU,+,ALU→A②实现减法时应提供以下控制信号:A→ALU,B*→ALU,ALU+1,+,ALU→A\n并行加法器由知令\n小结定点补码加减法运算方法,理解减法运算用加法来实现三种溢出检测方法及溢出判断的逻辑表达式基本加法器:半加器,全加器中和及进位的表达式、理解电路实现\n作业55-1.两个定点补码数分别放在寄存器A,B中,A0,B0是符号位,试列出两数运算的溢出判断条件。5-2.用补码运算求x-y,并判断是否溢出。x=-0.0100,y=0.1001x=-0.1011,y=-0.10105-3.已知[x]补=1.1001,[y]补=1.1110,计算2[x]补+1/2[y]补,并判断结果是否溢出。\n5-4.用一位全加器设计一个4位8421BCD码加法器。当4位加地结果有进位或超过9时,需要做加6校正。用真值表法得到校正的条件。5-5.串行加法器和并行加法器有何不同?影响并行加法器的关键因素是什么?设低位来的进位信号为C0,请分别按下述两种方式写出C4,C3,C2,C1的逻辑表达式。(1)串行进位方式(2)并行进位方式\n问题分析手工乘法运算方法在计算机实现时面临的困难原码一位乘中,如何把乘法运算转化为加法运算的?原码一位乘中,需要多次通过加法运算和移位得到部分和,效率低,如何提高乘的效率?