- 13.86 MB

- 2022-07-29 发布

- 1、本文档由用户上传,淘文库整理发布,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,请立即联系网站客服。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细阅读内容确认后进行付费下载。

- 网站客服QQ:403074932

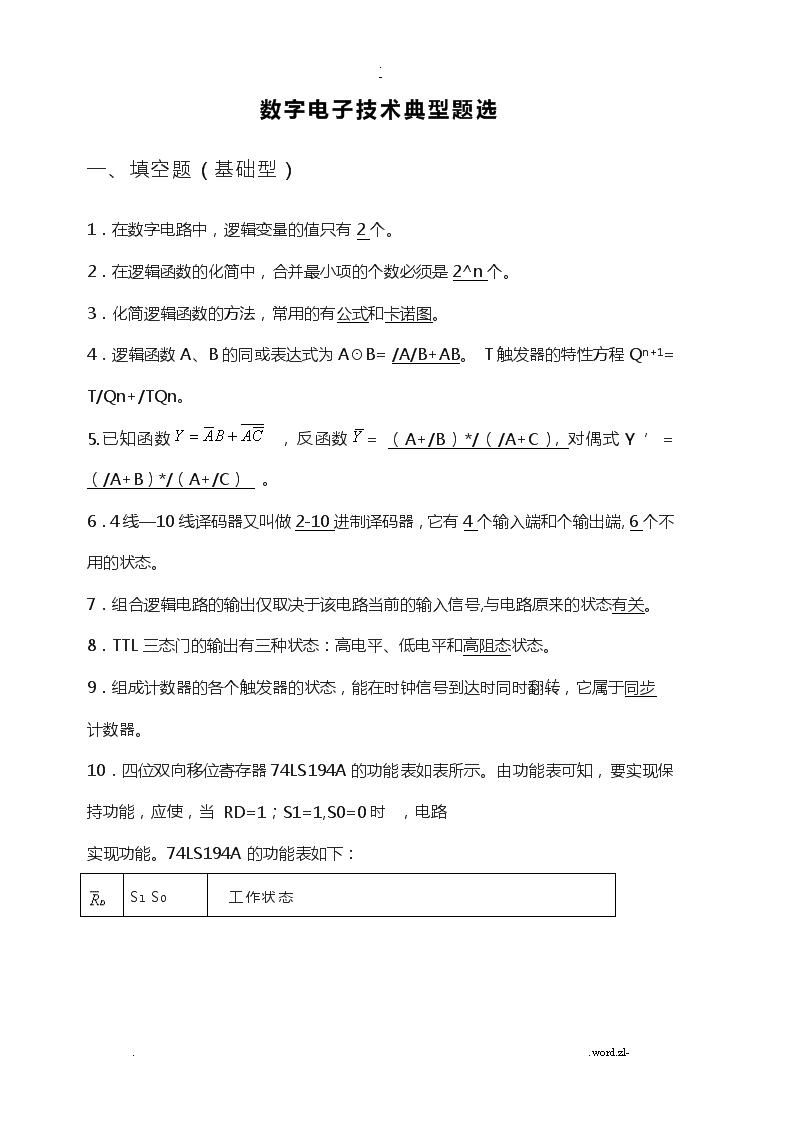

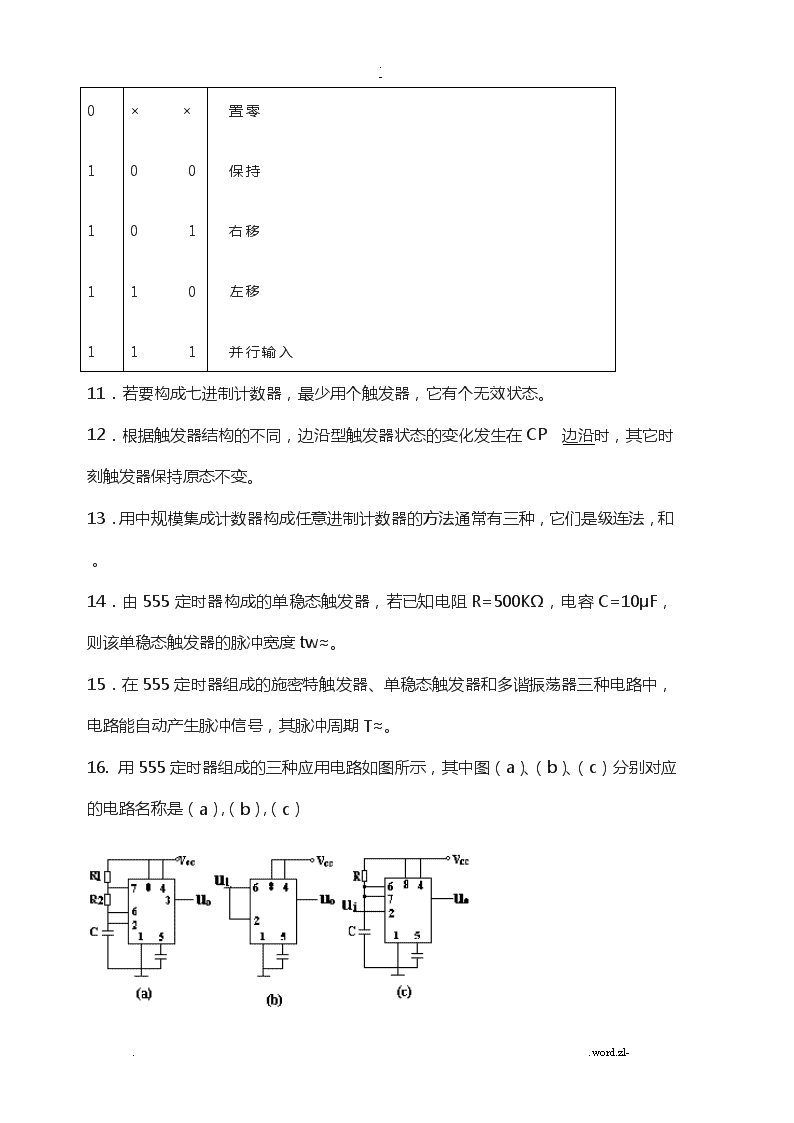

.-数字电子技术典型题选一、填空题(基础型)1.在数字电路中,逻辑变量的值只有2个。2.在逻辑函数的化简中,合并最小项的个数必须是2^n个。3.化简逻辑函数的方法,常用的有公式和卡诺图。4.逻辑函数A、B的同或表达式为A⊙B=/A/B+AB。T触发器的特性方程Qn+1=T/Qn+/TQn。5.已知函数,反函数=(A+/B)*/(/A+C),对偶式Y’=(/A+B)*/(A+/C)。6.4线—10线译码器又叫做2-10进制译码器,它有4个输入端和个输出端,6个不用的状态。7.组合逻辑电路的输出仅取决于该电路当前的输入信号,与电路原来的状态有关。8.TTL三态门的输出有三种状态:高电平、低电平和高阻态状态。9.组成计数器的各个触发器的状态,能在时钟信号到达时同时翻转,它属于同步计数器。10.四位双向移位寄存器74LS194A的功能表如表所示。由功能表可知,要实现保持功能,应使,当RD=1;S1=1,S0=0时 ,电路实现功能。74LS194A的功能表如下: S1S0工作状态..word.zl-\n.-01111××00011011置零保持右移左移并行输入11.若要构成七进制计数器,最少用个触发器,它有个无效状态。12.根据触发器结构的不同,边沿型触发器状态的变化发生在CP边沿时,其它时刻触发器保持原态不变。13.用中规模集成计数器构成任意进制计数器的方法通常有三种,它们是级连法,和 。14.由555定时器构成的单稳态触发器,若已知电阻R=500KΩ,电容C=10μF,则该单稳态触发器的脉冲宽度tw≈。15.在555定时器组成的施密特触发器、单稳态触发器和多谐振荡器三种电路中,电路能自动产生脉冲信号,其脉冲周期T≈。16.用555定时器组成的三种应用电路如图所示,其中图(a)、(b)、(c)分别对应的电路名称是(a),(b),(c)..word.zl-\n.-17.A/D转换器的转换过程包括,,,四个步骤。一、填空题(综合提高型)1.施密特触发器有2个稳定状态.,单稳态触发器有1个稳定状态.,多谐振荡器有0个稳定状态。2.欲对160个符号进行二进制编码,至少需要位二进制数;16路数据分配器,其地址输入端有个;2n选1的MUX,其地址端有______个,其数据输入端有_________个.3.欲构成可将1kHZ的脉冲转化为50HZ的脉冲的分频器,该电路至少需要用5个触发器;该电路共有20个有效状态。某计数器的状态转换图如图所示,该计数器为进制法计数,它有个有效状态,该电路(有或无)自启动能力?4.随机存储器RAM的电路结构主要由、和三部分组成。为构成4096×8的RAM,需要片1024×4的RAM芯片,并需要用位地址码以完成寻址操作。5.8位移位寄存器,串行输入时经个CP脉冲后,将得到8位数据的并行输出;欲将其串行输出,需经个CP脉冲后,数码才能全部输出。6.分别写出图1(a)、(b)、(c)、(d)所示电路中的输出函数表达式:Y1=Y2=/(AB);Y3=/(AB);Y4=/(AB)*/(BC);..word.zl-\n.-7.如图所示电路的逻辑表达式,F=1时的全部输入变量取值组合有12个.8.如图2所示的组合逻辑电路中的74138为3线-8线译码器,写出图2所示电路中各输出函数的最简与或表达式:F1=Y0+Y1+Y2=F2=Y4+Y7=9.图3是某ROM存储阵列的点阵图,A3、A2、A1、A0为地址线,D3、D2、D1、D0为数据线。试分别写出D3、D2、D1关于A3、A2、A1、A0的逻辑表达式。图中的点‘·’表示在行线和列线交叉处连接了存储元件。..word.zl-\n.-图310.由四位并行进位加法器74LS283如图所示,当A=0时,X3X2X1X0=0111,Y3Y2Y1Y0=0100,Z3Z2Z1Z0=_____________,W=_____________。电路功能为有符号数求和运算(加减运算):;A=0时:Z=X+Y=1011;W=Co=0;..word.zl-\n.- 二、选择题:请将正确答案的序号填在横线上。1.下列一组数中,是等值的。①(A7)16②(10100110)2③(166)10A.①和③B.②和①C.②和③2.在逻辑函数中的卡诺图化简中,若被合并的最小项数越多(画的圈越大),则说明化简后。A.乘积项个数越少B.实现该功能的门电路少C.该乘积项含因子少3.指出下列各式中哪个是四变量A、B、C、D的最小项()A、ABC; B、A+B+C+D; C、ABCD; D、A+B+D4.的最小项之和的形式是。A.B.C.5.在下列各种电路中,属于组合电路的有。A.编码器B.触发器C.寄存器6.74LS138是3线-8线译码器,译码输出为低电平有效,若输入A2A1A0=100时,输出=。A.00010000,B.11101111C.111101117.8线—3线优先编码器74LS148的优先权顺序是I7,I6,……I1,I0,输出Y2Y1..word.zl-\n.-Y0,输入低电平有效,输出为三位二进制反码输出。当I7I6,……I1I0为11100111时,输出Y2Y1Y0为。A.011B.100C.1108.在以下各种电路中,属于时序电路的有。A.反相器B.编码器C.寄存器D.数据选择器9.RS触发器当R=S=0时,Qn+1=。A.0B.1C.QnD.Q10.施密特触发器常用于对脉冲波形的。A.延时和定时B.计数与寄存C.整形与变换11.CPLD是基于,FGPA是基于A乘积项,查找表 B查找表,乘积项C乘积项,乘积项 D查找表,查找表12.以下单元电路中,具有“记忆”功能的单元电路是A、加法器;B、触发器;C、TTL门电路;D、译码器;13.对于CMOS与门集成电路,多余的输入端应该A接高电平B接低电平C悬空D接时钟信号如果TTL电路的输入端开路,相当于接入A逻辑1B逻辑0C无法预测D有可能是逻辑1,也有可能是逻辑0。14..摩根定律(反演律)的正确表达式是:A、B、C、D、.15.JK触发器实现T触发器的功能时,J,K应该怎样连接A.J=K=TB.J=K=D.C.J=0,K=1D.J=D,K=16.同步时序电路和异步时序电路比较,其差异在于后者。A.没有触发器B.没有统一的时钟脉冲控制C.没有稳定状态D.输出只与内部状态有关17.要使JK触发器的输出Q从1变成0,它的输入信号JK应为()。A.00B.01C.10D.无法确定18.对于T触发器,若原态Qn=1,欲使新态Qn+1=1,应使输入T=。..word.zl-\n.-A.0B.1C.QD.19.下列触发器中,没有约束条件的是。A.基本RS触发器B.主从RS触发器C.同步RS触发器D.边沿D触发器20.逻辑函数的表示方法中具有唯一性的是。A.真值表B.表达式C.逻辑图D.卡诺图21.8—3线优先编码器(74LS148)中,8条输入线~同时有效时,优先级最高为I7线,则输出是()A.000B.010C.101D.11122.七段显示译码器是指()的电路。A.将二进制代码转换成0~9个数字B.将BCD码转换成七段显示字形信号C.将0~9个数转换成BCD码D.将七段显示字形信号转换成BCD码23.逻辑数F=A+A+B,当变量的取值为()时,将出现冒险现象。A.B=C=1B.B=C=0C.A=1,C=0D.A=0,B=024.用n个触发器构成计数器,可得到最大计数模值是()A.nB.2n-1C.2nD.2n-1三、逻辑函数化简与变换:1.试求逻辑函数F的反函数的最简与或式,并用与或非门实现电路解:..word.zl-\n.-2.证明下列各逻辑函数式:左式=====右式原式成立3.将下列逻辑函数化简成最简与或及与非-与非表达式(答案略) 四.组合逻辑电路的分析与设计1、4选1数据选择器74LS153的功能表达式为 :试写出下图电路输出z的逻辑函数式。/A/B+/AC+A/C..word.zl-\n.-2、设计一位8421BCD码的判奇电路,当输入码中,1的个数为奇数时,输出为1,否则为0。(1)画出卡诺图,并写出最简“与-或表达式”;(2)用一片8选1数据选择器74LS151(功能符号见图)加若干门电路实现,画出电路图。解:(1)卡诺图:最简“与-或式”:;(2)电路图:..word.zl-\n.-3、某组合逻辑电路的芯片引脚图如题图所示。1.分析题图所示电路,写出输出函数F1、F2的逻辑表达式,并说明该电路功能。2.假定用四路数据选择器实现题图所示电路的逻辑功能,请确定下图所示逻辑电路中各数据输入端的值,画出完善的逻辑电路图。解:1.写出电路输出函数F1、F2的逻辑表达式,并说明该电路功能。该电路实现全减器的功能功能。..word.zl-\n.-2.假定用四路数据选择器实现该电路的逻辑功能,请确定给定逻辑电路中各数据输入端的值,完善逻辑电路。4.3线-8线译码器74LS138逻辑功能表达式为,,……,,,正常工作时,S1=1,S2=S3=0。1、试写出Z1和Z2的逻辑函数式。..word.zl-\n.-5、用3线-8线译码器74LS138芯片设计一位全加器,可附加门电路,要求写出真值表、逻辑表达式,画出逻辑电路图。解:真值表(略).逻辑表达式如下:逻辑电路图如下:6.试用最少的与非门设计实现一个一位十进制数(用8421BCD码表示)的四舍五入电路,当数码大于等于5时输出为1,否则输出为0。要求列出真值表、卡诺图,写出最简表达式,并画出逻辑电路图:(1)直接用门电路实现;(2)用两片3-8线译码器74138实现;(3)用4-1MUX及必要的门电路实现。解:逻辑表达式为:(1);(2)(3)答案略,自己做!..word.zl-\n.-7、由四位并行进位加法器74LS283构成下图所示电路:(1).当A=0时,X3X2X1X0=0011,Y3Y2Y1Y0=0100求Z3Z2Z1Z0=?,W=?(2)当A=1时,X3X2X1X0=1001,Y3Y2Y1Y0=0101求Z3Z2Z1Z0=?,W=?(3)写出X(X3X2X1X0)、Y(Y3Y2Y1Y0)、A与Z(Z3Z2Z1Z0)、W之间的算法公式,并指出其功能。解:(1)A=0时:Z=X+Y=0111;W=Co=0;(2)A=1时:=0100;;(3)电路功能为有符号数求和运算(加减运算):;8、用74283及门电路构成一位8421BCD码加法器解:大于9或有进位输出,就加6同时输出进位..word.zl-\n.-五.画触发器电路时序图1、试画出如图所示电路在输入波形CP、及D作用下Q1及Q2的输出波形.设电路初态Q1Q2=11,且不计传输时延.解:..word.zl-\n.-2、在数字系统设计时,常用如下左图所示电路来检测输入信号的上升沿,已知输入信号Din如下右图所示,设触发器初态为0,请画出检测输出信号DECT波形。3、试对图5所示电路在输入波形作用下,画出相应的输出波形(假设初态Q1Q2=00)...word.zl-\n.-六.时序逻辑电路分析与设计1、试分析如图所示的时序逻辑电路,要求:(1)列出驱动方程、状态方程(2)Q2、Q1、Q0状态表,画出状态图(3)画出在CP脉冲作用下三个触发器的状态信号和Y的波形图,设三个触发器的初态均为0。解:(1)驱动方程:J0=K0=1J1=K1=J2=K2=(2)状态表Q2nQ1nQ0nQ2n+1Q1n+1Q0n+1..word.zl-\n.-000001001010010011011100100101101110110111111000触发器构成模8计数器,数据选择器74151产生所需序列100011112、如图6所示电路中X为控制端;试分析当X=0和X=1时电路的逻辑功能;写出驱动方程、状态方程和状态图,并画出当X=1时的时序图;(设初始状态Q1Q0=11)。解:输出方程和激励方程:状态方程..word.zl-\n.-状态图当外部输入X=0时,状态转移按00→01→10→11→00→…规律变化,实现模4加法计数器的功能;当X=1时,状态转移按00→11→10→01→00→…规律变化,实现模4减法计数器的功能。所以,该电路是一个同步模4可逆计数器。X为加/减控制信号,Z为借位输出3、分析如题图所示时序逻辑电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。并说明电路能否自启动(设初始状态均为零)。..word.zl-\n.-解:略,自行分析!4、电路如题图所示,其中RA=RB=10kΩ,C=0.1μf,试问:1).在Uk为高电平期间,由555定时器构成的是什么电路,其输出U0的频率f0=?2).分析由JK触发器FF1、FF2、FF3构成的计数器电路,要求:写出驱动方程和状态方程,列出状态转换表,画出完整的状态转换图;3).设Q3、Q2、Q1的初态为000,Uk所加正脉冲的宽度为Tw=6/f0,脉冲过后Q3、Q2、Q1将保持在哪个状态?..word.zl-\n.-解:1).多谐振荡器f0=476Hz;2).写出驱动方程、状态方程,列出状态转换000->100->110->111->011->001->回到100;3).Q3Q2Q1=100;4、画出题图(a)、(b)的状态转换图,分别说明它们是几进制计数器。..word.zl-\n.-解:11进制,12进制,67进制5、同步4位二进制集成计数器CT74161的常用符号和功能表如图示1).说明图示电路为几进制计数器,并画出其主循环状态图;2).用反馈清零法将其构成一个同步38进制计数器。CRLDCLKETEPQ3Q2Q1Q00X↑XX000010↑XXD3D2D1D011↑11计数11X0X保持11XX0保持解:1)7进制2)先同步级联再反馈清零,..word.zl-\n.-清零逻辑:CR=Q5Q2Q1(38=00100110)图略6、给出同步十进制集成计数器CT74160的功能表。74LS138为3线—8线译码器;(1)说明题图所示电路中CT74160构成的是几进制计数器?并画出其有效循环状态图;(2)画出在图8给定的CP脉冲作用下输出Y的波形图(3)用整体清零法将两片CT74160构成一个同步36进制BCD码计数器。解:(1)5进制,0000—0001—0010—0011—0100—0000(2)(3)先同步级联再反馈清零,清零逻辑:CR=Q5Q4Q2Q1(0011,0110)..word.zl-\n.-7、在图示电路中,Ra、Rb、R1、R2分别为四个4位移位寄存器,其移位方向如图示为右移,设Ra、Rb内已存有二进制数码(见图),则在第四个CP脉冲作用后,移位寄存器R1中的数码为,R2中的数码为;8.试用JK触发器设计一个同步三进制加法计数器。解:状态图如下:000110..word.zl-\n.-Q1Q0由K图得Q1n+1=Q0n;Q0n+1=/Q1n*/Q0n得:J1=Q0n,K1=/Q0;J0=/Q1n,K0=1七.现有如下图所示的4×4字位容量RAM若干片,如需把它们扩展成8×8字位RAM。1).试问需用几片4×4字位容量RAM?2)画出扩展后的电路图(可用少量与非门)。解:1)用4×4RAM扩展成8×8RAM时,需要进行字扩展和位扩展,所以需要4片4×4RAM。2.扩展后电路如图..word.zl-\n.-八.脉冲波形的产生与整形1、图示电路是由555定时器和计数器构成的一个定时电路,试回答下列问题:(1)电路中555定时器接成何种电路?(2)设计数器的初态为Q3Q2Q1Q0=0000,当开关S接通后经过多少时间发光二极管LED变亮?..word.zl-\n.-(1)多谐震荡器(2)1720S2、如图vi为施密特反相器输入信号,请画出输出信号vo波形。解:3、所示电路是由555定时器构成的施密特触发器,VCC=12V,C1=0.01µF。(1)计算VT+、VT-及回差电压(2)画出Uo的波形。..word.zl-\n.-解:VT+=8V,VT-=4V及回差电压=4V。4、由5G555构成的多谐振荡器如图所示。1)说明A的逻辑值为何值时,电路起振;2)设R1、R2、C为已知,求UO的振荡频率;3)求波形的占空比。..word.zl-\n.-..word.zl-