- 68.00 KB

- 2022-07-29 发布

- 1、本文档由用户上传,淘文库整理发布,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,请立即联系网站客服。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细阅读内容确认后进行付费下载。

- 网站客服QQ:403074932

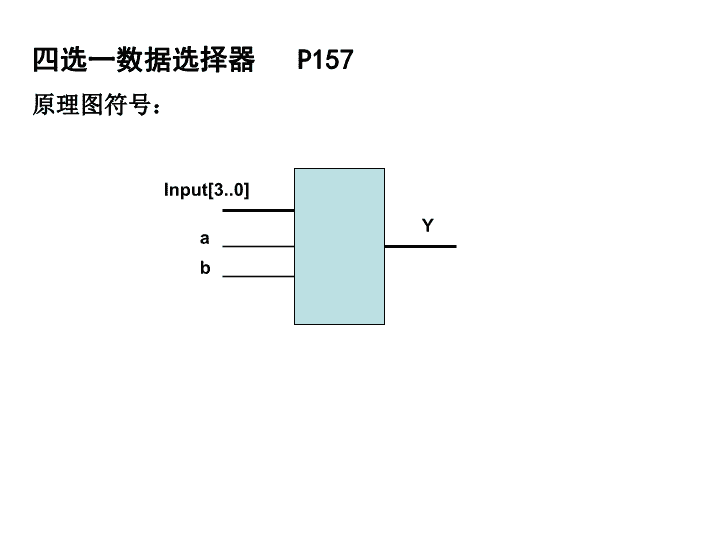

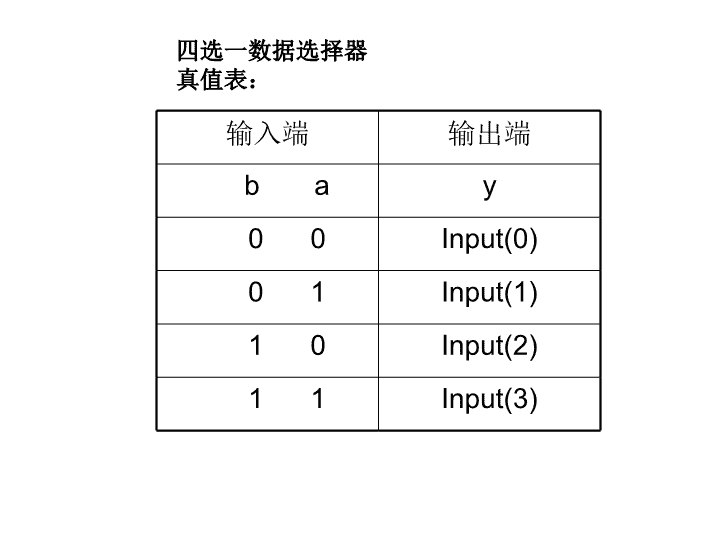

Input[3..0]Y四选一数据选择器P157原理图符号:ab\n四选一数据选择器真值表:输入端输出端bay00Input(0)01Input(1)10Input(2)11Input(3)\n8-3线优先编码器\n\n8-3线优先编码器真值表(反码编码方案)输入端低电平有效,优先级高→低输出端为反码输入输出Input7input6input5input4input3input2input1input0Output2output1output00xxxxxxx00010xxxxxx001110xxxxx0101110xxxx01111110xxx100111110xx1011111110x11011111110111\nLIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYcoderISPORT(input:INSTD_LOGIC_VECTOR(0TO7);output:OUTSTD_LOGIC_VECTOR(0TO2));ENDcoder;ARCHITECTUREbehavOFcoderISBEGINPROCESS(input)BEGINIFinput(7)='0'THENoutput<="000";ELSIFinput(6)='0'THENoutput<="100";ELSIFinput(5)='0'THENoutput<="010";ELSIFinput(4)='0'THENoutput<="110";ELSIFinput(3)='0'THENoutput<="001";ELSIFinput(2)='0'THENoutput<="101";ELSIFinput(1)='0'THENoutput<="011";ELSEoutput<="111";ENDIF;ENDPROCESS;ENDbehav;\nq[3..0]4位二进制码表示clk输入的脉冲个数具有清零端的四位二进制计数器P156原理图符号:时钟脉冲输入clk(接125引脚)高电平清零clr\nclr=1q=0000clr=0:输入CLK输出Q3Q2Q1Q00000000100100011●●●●●●\n4位二进制计数器计数器设计libraryieee;useieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entitycnt4isport(clk:instd_logic;clr:instd_logic;q:bufferstd_logic_vector(3downto0));Endcnt4;architecturebehavofcnt4isbeginprocess(clr,clk)beginifclr=‘1’thenq<=“0000”;elsifclk'eventandclk='1'thenq<=q+1;endif;endprocess;Endbehav;