- 188.32 KB

- 2022-07-30 发布

- 1、本文档由用户上传,淘文库整理发布,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,请立即联系网站客服。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细阅读内容确认后进行付费下载。

- 网站客服QQ:403074932

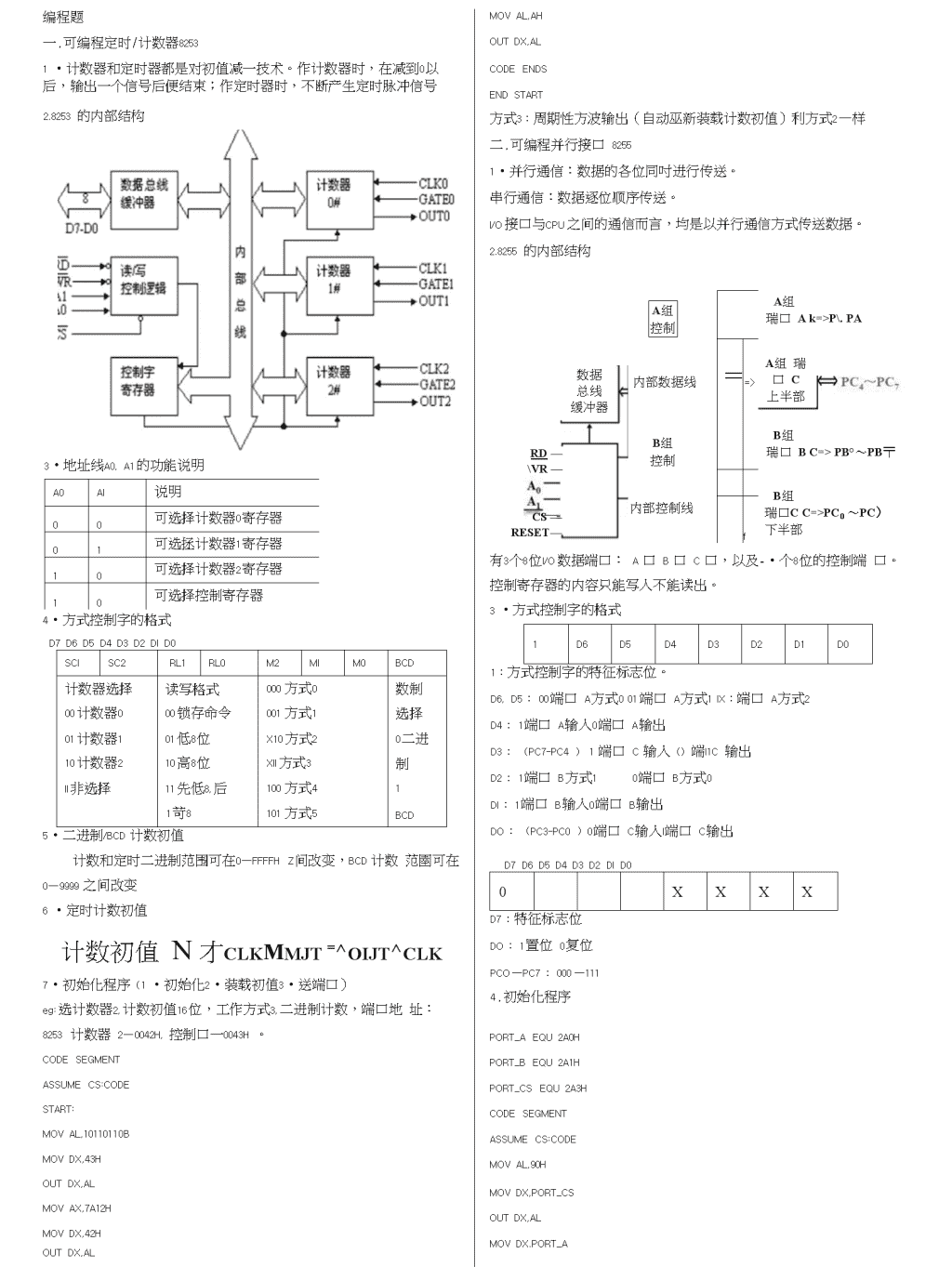

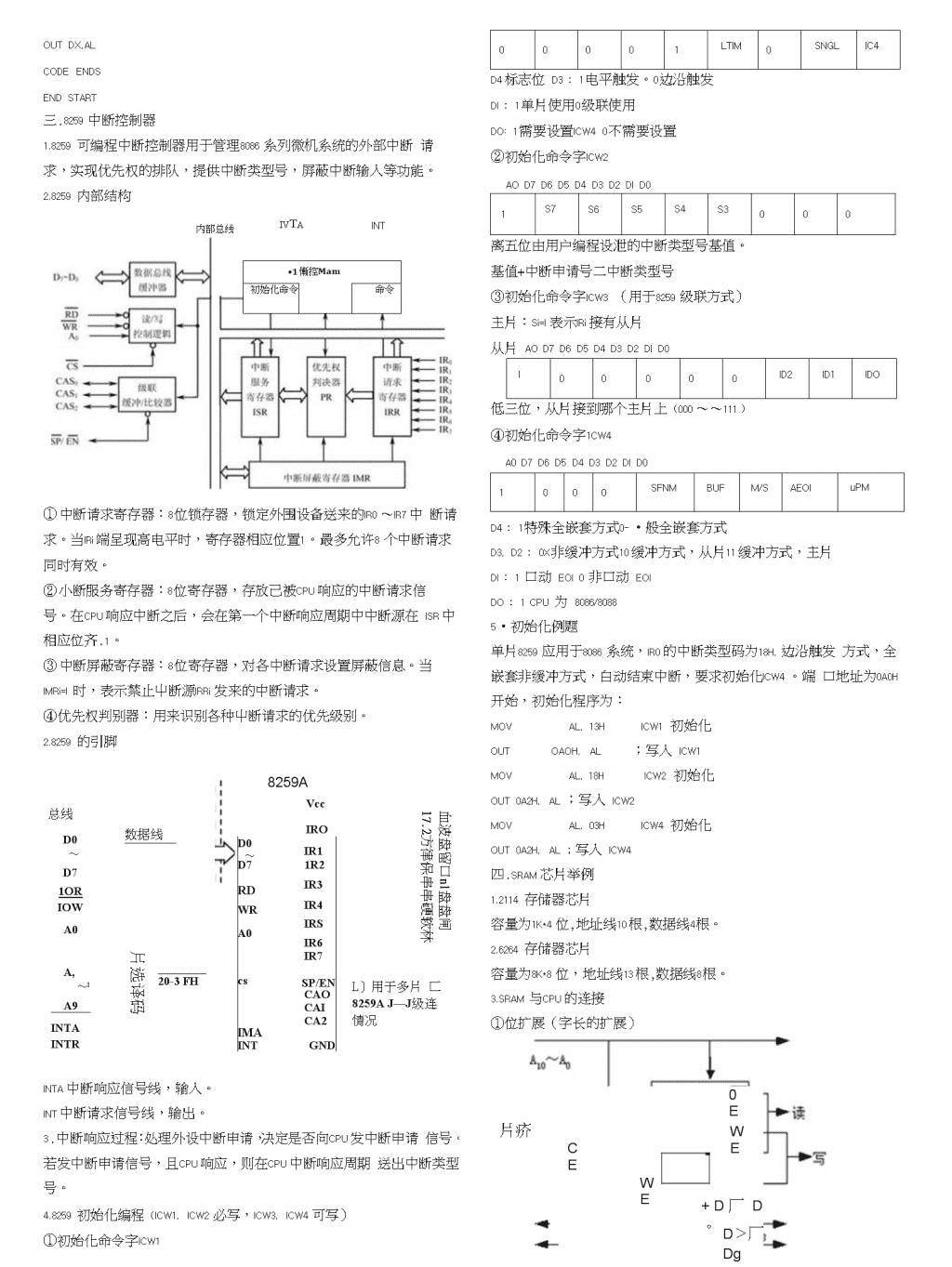

2.8253的内部结构A0Al说明00可选择计数器0寄存器01可选拯计数器1寄存器10可选择计数器2寄存器10可选择控制寄存器3•地址线A0,A1的功能说明4•方式控制字的格式A组控制RD—\VR—内部数据线内部控制线B组控制CS—RESET—数据总线缓冲器==>fA组瑞口Ak=>P\.PAB组瑞口BC=>PB°〜PB〒B组瑞口CC=>PC0〜PC)下半部A组瑞口C上半部编程题一.可编程定时/计数器82531•计数器和定时器都是对初值减一技术。作计数器时,在减到0以后,输出一个信号后便结束;作定时器时,不断产生定时脉冲信号D7D6D5D4D3D2DID0SCISC2RL1RL0M2MlM0BCD计数器选择读写格式000方式0数制00计数器000锁存命令001方式1选择01计数器101低8位X10方式20二进10计数器210高8位XII方式3制II非选择11先低8,后100方式411苛8101方式5BCD5•二进制/BCD计数初值计数和定时二进制范围可在0—FFFFHZ间改变,BCD计数范圉可在0—9999之间改变6•定时计数初值计数初值N才clkMmjt=^oijt^clk7•初始化程序(1•初始化2•装载初值3•送端口)eg:选计数器2,计数初值16位,工作方式3,二进制计数,端口地址:8253计数器2—0042H,控制口一0043H。CODESEGMENTASSUMECS:CODESTART:MOVAL,10110110BMOVDX,43HOUTDX,ALMOVAX,7A12HMOVDX,42HOUTDX,ALMOVAL,AHOUTDX,ALCODEENDSENDSTART方式3:周期性方波输出(自动巫新装载计数初值)利方式2—样二.可编程并行接口82551•并行通信:数据的各位同吋进行传送。串行通信:数据逐位顺序传送。I/O接口与CPU之间的通信而言,均是以并行通信方式传送数据。2.8255的内部结构有3个8位I/O数据端口:A口B口C口,以及-•个8位的控制端口。控制寄存器的内容只能写入不能读出。3•方式控制字的格式1D6D5D4D3D2D1D01:方式控制字的特征标志位。D6,D5:00端口A方式001端口A方式1IX:端口A方式2D4:1端口A输入0端口A输出D3:(PC7-PC4)1端口C输入()端I1C输出D2:1端口B方式10端口B方式0DI:1端口B输入0端口B输出DO:(PC3-PC0)0端口C输入I端口C输出D7D6D5D4D3D2DID00XXXXD7:特征标志位DO:1置位0复位PCO—PC7:000—1114.初始化程序PORT_AEQU2A0HPORT_BEQU2A1HPORT_CSEQU2A3HCODESEGMENTASSUMECS:CODEMOVAL,90HMOVDX,PORT_CSOUTDX,ALMOVDX.PORT_A\nINAL,DX\nOUTDX,ALCODEENDSENDSTART三.8259中断控制器1.8259可编程中断控制器用于管理8086系列微机系统的外部中断请求,实现优先权的排队,提供中断类型号,屏蔽中断输入等功能。2.8259内部结构00001LTIM0SNGLIC4D4标志位D3:1电平触发。0边沿触发DI:1单片使用0级联使用DO:1需要设置ICW40不需要设置②初始化命令字ICW2AOD7D6D5D4D3D2DID0内部总线1S7S6S5S4S3000离五位由用户编程设泄的中断类型号基值。基值+中断申请号二中断类型号③初始化命令字ICW3(用于8259级联方式)主片:Si=l表示IRi接有从片从片AOD7D6D5D4D3D2DID0•1慚控Mam初始化命令命令ivTaINT①中断请求寄存器:8位锁存器,锁定外围设备送来的IR0〜IR7中断请求。当IRi端呈现高电平时,寄存器相应位置1。最多允许8个中断请求同时有效。②小断服务寄存器:8位寄存器,存放己被CPU响应的中断请求信号。在CPU响应中断之后,会在第一个中断响应周期中中断源在ISR中相应位齐.1。③中断屏蔽寄存器:8位寄存器,对各中断请求设置屏蔽信息。当IMRi=l时,表示禁止屮断源IRRi发来的中断请求。④优先权判别器:用来识别各种屮断请求的优先级别。2.8259的引脚总线D0〜D71ORIOWA0A,〜1A9INTAINTR数据线8259AI00000ID2ID1IDO低三位,从片接到哪个主片上(000〜〜111)④初始化命令字1CW4A0D7D6D5D4D3D2DID01000SFNMBUFM/SAEOIuPM片选译码20-3FHD0〜IR1D71R2RDIR3WRIR4A0IRSIR6csIR7SP/ENCAOCAICA2IMAINTGNDL]用于多片匚8259AJ—J级连情况VccIRO血波盘留口nl盘盘闸17.2方律保串串硬软林D4:1特殊全嵌套方式0-•般全嵌套方式D3,D2:0X非缓冲方式10缓冲方式,从片11缓冲方式,主片DI:1口动EOI0非口动EOIDO:1CPU为8086/80885•初始化例题单片8259应用于8086系统,IR0的中断类型码为18H,边沿触发方式,全嵌套非缓冲方式,白动结束中断,要求初始化ICW4。端口地址为0A0H开始,初始化程序为:MOVAL,13HICW1初始化OUTOAOH,AL;写入ICW1MOVAL,18HICW2初始化OUT0A2H,AL;写入ICW2MOVAL,03HICW4初始化OUT0A2H,AL;写入ICW4四.SRAM芯片举例1.2114存储器芯片容量为1K*4位,地址线10根,数据线4根。2.6264存储器芯片容量为8K*8位,地址线13根,数据线8根。3.SRAM与CPU的连接①位扩展(字长的扩展)INTA中断响应信号线,输入。INT中断请求信号线,输出。3.中断响应过程:处理外设中断申请,决定是否向CPU发中断申请信号。若发中断申请信号,且CPU响应,则在CPU中断响应周期送出中断类型号。4.8259初始化编程(ICW1,ICW2必写,ICW3,ICW4可写)①初始化命令字ICW1片疥0EWECE+D厂D。D>厂DgWE\nAH:ALBH:BLCH:CLDH:DL15870SID【BPSPFLAGSIP雯址耐o代砾耐数竭段韶老存储芯片的地址线,片选信号线以及控制信号线并联。数据线按数据位的高低顺序分别连到数据总线上。存储器芯片的地址线,数据线,读写控制信号线均并联。片选信号是各口独立被选中。4.存储器容彊为1KB,需地址线10根存储器容量为2KB,需地址线11根存储器容量为8KB,需地址线13根5•字位全扩展(位和字同时(串并联)扩充)当存储器的位数和单元数都需要扩充时,则可以先扩充位数,然后再扩充单元数。①根据内存容量及芯片容量确定所需存储芯片数;②进行位扩展以满足字长要求;③进行字扩展以满足容量要求。④若已有存储芯片的容量为LXK,要构成容量为MXN的存储器,需要的芯片数为:(M/L)X(N/K)用2114(1K*4)RAM芯片构成4K*8存储器第二章8086CPU结构AX累鳩BX基址前丑CX计数器dx目的地址爲存器基址指针堆桜指针标志寄存器指令描针1.标志寄存器(只用9个,6个状态标志位,3个控制标志位)15141312II1098765432I0OFDFIFTFSFZFAFPFClCF进位标志,运算结果的最高D7产牛进位或借位则CF=1PF奇偶标志,运算结果的低八位中含有偶数个1,则PF=1AF辅助进位,结果低4位向高4位产生进位或借位,AF=1ZF零标志,结果为0,则ZF=1SF符号标志,运算时最高位为1,则SF=1OF溢岀标志,补码运算有溢岀时,OF=12.8086微处理器冇最小模式和最大模式。最小模式:用于由8086单一微处理器构成的小系统,其总线控制逻辑全部直接由8086CPU产生和控制。最大模式:用丁实现多处理机系统。8086CPU是主处理器,其他处理器称为协处理器。总线控制逻辑由总线控制器8288产生和控制,即8288对主处理器的状态与信号进行译码产生相应的控制信号和系统总线命令,从而接受并执行来自主处理器的命令,协助其完成某些辅助工作。3.—条指令的执行包括取指令,分析指令,执行指令。4.8086CPU时序时序:时序是计算机操作运行的时间顺序。时钟周期:CPU时钟频率的倒数称为时钟周期,也称T状态。总线周期:BIU完成一次访问存储器或I/O端口操作所需要的时间称为总线周期。一个基本的总线周期是由4(或4个以上)时钟周期组成的。指&周期;执行一条指令所需要的时间称为指令周期,不同指令的指令周期的长短是不同的。一个指令周期是由儿个总线周期组成的。一个基本的总线周期的4个T状态第三章寻址方式与指令系统1.物理地址=段址T6+段内的偏移量2.8086寻址方式立即数寻址(无物理地址)MOVAX,251寄存器寻址(无物理地址)MOVAX,DX直接寻址MOVAX,[1000H]PA=16*DS+1000H寄存器间接寻址MOVAX,[BX]PA=16*DS+BX寄存器是BX,SI,DI,则默认DS。BP默认SS。寄存器相对寻址MOVAX,20H[SI]PA=DS*16+SI+20HMOVCL,[BP+2000H]PA=SS*16+BP+2000H基址加变址寻址MOVAX,[BX][SI]PA=DS*16+BX+SI相对基址加变址寻址MOVAX,[BX+DI+20H]第六章中断方式1.无条件传送:外设已处于就绪状态,玄接执行I/O指令进行数据传输。仅传输数据信息,不传输控制状态信息。2•条件传送:CPU不断查询相应设备的状态,状态信号符合时进行操作。要传输数据,控制状态信息。3.不可屏蔽中断:由NM1引脚引入,它不受中断允许标志位的影响,每个系统中仅允许有一个,都用来处理紧急情况。4•可屏蔽中断:由INIR引脚引入,它受中断允许标志位的影响,当IF=1时,可屏蔽屮断才能进入,可屏蔽中断冇多个,一般通过优先级排队。5•中断传送方式:利用CPU本身的中断功能和I/O接口的中断功能來实现对外设I/O数据的传送。6•中断的定义:中断是外设或英他中断源中止CPU当前正在执行程序而转向该外设服务的程序,一旦程序结束,又返回原程序继续。7.中断源:能够引发中断的事件或原因被称为中断源,或发出中断屮请的来源。内部中断源和外部中断源。\n7.屮断向最:由屮断类型号来查找屮断入口地址进而转向屮断服务程序的方法称为屮断向最。(段基址CS和偏移地址IP)8.屮断向最表(首地址默认为00000H)地址为00000H-003FFH中断向量表需占用256*4=1K字节的地址空间。0003FHIOOOOOSH000007H00000411000003H000002HOOOOOIHOOOOOOK中FF图5.21中慚向愉表屮断矢量号N中断服务程序的入口地址(CS,IP)*4中断矢:ft表的地址中断矢虽表10.屮断嵌套:允许高优先级的屮断申请打断低级中断处理程序的执行。条件:CPU开中断,有级别更高的中断源请求。二、简答题1.将10011100和11100101相加后,CF、PF、AF、ZF、SF、0F各为何值?解:10011100+11100101=110000001CE:进位标志(D7向D8产生进位或借位,贝iJCl-1)C1-1;PF:奇偶标志位(低八位中含偶数个1,则PF=1)PF=1;AF:辅助进位标志(D3向D4产生进位或借位,贝ljAF=1)AF=1;ZF:(零标志位)ZF=O;SF:符号标志位(D7或D15为1,则SF=1)SF=1;OF:溢出标志位(运算结果超出字节运算:80ir7EH或字运算:8000H~7FFFH,贝lj0F=l)OF=01.简述8086微处理器冇哪几种工作模式?各冇什么特点?答:8086微处理器有最小模式和最大模式。①故小模式特点:用于只由8086微处理器构成的小系统,其总线控制逻辑全部直接由8086CPU产生和控制。②最人模式特点:用于实现多处理机系统。8086CPU是主处理器,其他处理器称为协处理器。总线控制逻辑由总线控制器8288产生和控制,即8288对主处理器的状态与信号进行译码产生相应的控制信号和系统总线命令,从而接受并执行來自主处理器的命令,协助其完成某些辅助工作。2.某微机冇4级中断,共中断响应及处理优先级从高到低为1-2-3-4(即1级最高,4级最低),假定在执行用户程序过程中,同吋出现2级和3级中断请求,而在处理2级中断过程中,乂同时出现1级和4级屮断请求,试问各级屮断处理完成的顺序是什么?请画出处理该多重中断示意图。答:中断处理流程如图所示:3.简述存储器的性能指标?答:存储器的性能指标:存储器容虽、存取周期功耗、可靠性、集成度存储器容量:存储器所能容量的故大字节数。存储1位二进制信息的单元是1个存储单元。存储器芯片容量二单元数X位数存取周期:从接收到地址,到实现-•次完整的读出或坷入数据的时间,是存储器进行连续读或写操作所允许的最短时间间隔。4.什么是中断类型码、中断向量、中断向量表?在基于8086/8088的微机系统中,中断类型码和屮断向量之间冇什么关系?答:中断类型码:处理机可处理的每种中断的编号,每个中断源都冇唯一的一个中断识别号中断向量:中断处理程序的入口地址,由处理机自动寻址。中断向量表:用于顺序存放所有类型中断处理程序入口地址的一个默认的内存区域。中断类型码乘以4得中断向彊表的入口地址,从此处可读出4字节内容即为中断向戢。5.简述可屏蔽中断和不可屏蔽中断的特点?答:①不可屏蔽中断:由\MI线上的中断请求信号引起的中断,中断类型号是2。不可屏蔽中断NMI具有比可屏蔽中断INTR更高的优先权。即此中断是不受中断允许触发器IF状态的影响,不能被CPU用指令CI」来屏蔽。②可屏蔽中断:由TNTR线上的中断请求信号引起的中断。可屏蔽中断TNTR受中断允许触发器状态的影响,可用CLT指令来屏蔽(使120),用STT指令允许(使IF=l)oM中断请求信号必须保持到当前执行的指令结束为止。6.简述8086CPU的寄存器组织?解:8086微处理器内部共冇14个16位寄存器,分别是4个数据寄存器,4个段寄存器,4个地址指针与变址寄存器和2个控制寄存器。其寄存器组织如图:一、填空题1.微型计算机系统的主耍性能指标:①字长:微处理器内部一次性可以并行处理二进制代码的位数决定,其中位(bit)是计算机内部数据存储的最小单位②内存容量:内存容量是以字节为单位来度量容量的大小\n①指令系统④运行速度⑤容许配置的外设数量⑥系统软件的配置1.数制转换:-|•进制数转换成I•六进制数,即将十进制数先转换为二进制数,再将二进制数转换为十六进制数(每四位二进制码表示一位十六进制码,不足位整数部分高位补零,小数部分低位补零)①4.75②2.25③1.875解:①4.75=100.11B=4.CH②2.25=10.01B=2.4H③1.875=1.111B=1.EH2.每秒传送二进制数的位数是比特率(bit/s)3.微型计算机系统总线由数据总线(DB),地址总线(AB),控制总线(CB)三部分组成。4.常用的串行通信数据传送方式:单工方式,半双工方式和全工方式。5.CPU从存储器或外设获取一个字节或字所需要的吋间总线周期。6.微机对存储器和1/0设备进行编址的方式:1/0端口和存储器统一编址;1/0端口独立编址。7.8086CPU内部的两大独立功能部件分别是总线接口部件(B11)和执行部件(EU)o8.接口的概念:接口是CPU与外设之间连接的桥梁,实现两者Z间数据的传递和转换。9.最人模式的控制总线要由另外的芯片8288产生,最小模式的控制信号就有CPU自己产生。11•段寄存器CS=0100H,指令指针寄存器IP=1000H,此时,指令的物理地址为多少?指向这一物理地址的CS值和1P值是唯一的吗?解:逻辑地址二段基地址+段内偏移地址物理地址二段基值(16位)<<4+偏移量①・••物理地址=010011X16*100011=1000011②CS值和TP值不是唯一的12.8086CPU冇20根地址线,可直接寻址的存储物理空间是珂B,其地址范围是oooooirmTHi,物理地址和逻辑地址及其计算方法:逻辑地址二段基地址+段内偏移地址物理地址二段基值(16位)«4+偏移量13.当端口地址大于OFFH时,指令屮不能直接写端口地址,要借用DX寄存器来存储端口址。14.写出下列容量的RM1芯片片内的地址线和数据线的条数:(1)4KX8位;(2)512KX4位;(3)1MX1位;(4)2KX8位解(1)4K=2?x2^=2",则所需地址线12根,数据线8根(2)所需地址线19根,数据线4根(3)所需地址线20根,数据线1根(4)所需地址线11根,数据线8根二、读程序1.阅读程序段,分析程序功能。耍求写出每条指令运行后,相应寄存器或内存单元的内容。MOVBX,200011;(BX)=200011MOVAl.,5;(AL)=05HXLAT:AL=2005H注:XLAT指令的功能:(AL)-((BX)+(AL)),即AL与BX中的内容相加所得的结果作为新的访问地址,访问该地址所得的内容送给ALo2.阅读程序段,分析程序功能。己知X、Y、Z都是16无符号数,且运算过程中间结果都不超出16位二进制数的范围。MOVAX,X;取XADDAX,Y;(AX)二X+YMOVCX,3;(CX)=3MULCX;(DX:AX)=3*(X+Y)AX存放结果的低16位,DX存高16位MOVCX,AX;(CX)=3*(X+Y)MOVAX,Y;取YADDAX,Z;(AX)=Y+ZXORDX,DX:(DX)=OMOVBX,Y;取YSUBBX,Z;(BX)=Y-ZDTVBX;(AX)=(Y+Z)/(Y-Z)ADDAX,CX;(AX)=3*(X+Y)+(Y+Z)/(Y-Z)MOVSUM,AX;存结果3.已知CIIR字节单元冇一个二进制冇符号数X,编程计算Y,其结果存入PQ单元中。4X,X<5Y=\1X-&520DATASEGMENTC11RDB9•PQDB9■XEQUC11RYEQUPQDATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXMOVAL,XCMPAL,5JNL1ASHLAL,2;(AL)=4*X(AL)«1,即数值乘以2JMPL3LI:CMPAL,20;X>=20,则执行L2JNLL2MOVBL,71MULBLSUBAL,8JMPL3L2:MOVAL,50;XX20时,(AL)=50JMPL3L3:MOVY,ALCODEENDSENDSTART4.下面的4条指令,是一段为8251A进行初始化的程序,请按以下要求将程序补充完整:将这片8251A设置为异步传输方式,7位字符,偶校验,2个停止位,波特率因子16,发送和接收都允许。MOVAL,11111010B;工作方式字\nOUT42H,ALMOVAL,00110111B;控制字OUT4211,AL