- 132.73 KB

- 2022-07-30 发布

- 1、本文档由用户上传,淘文库整理发布,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,请立即联系网站客服。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细阅读内容确认后进行付费下载。

- 网站客服QQ:403074932

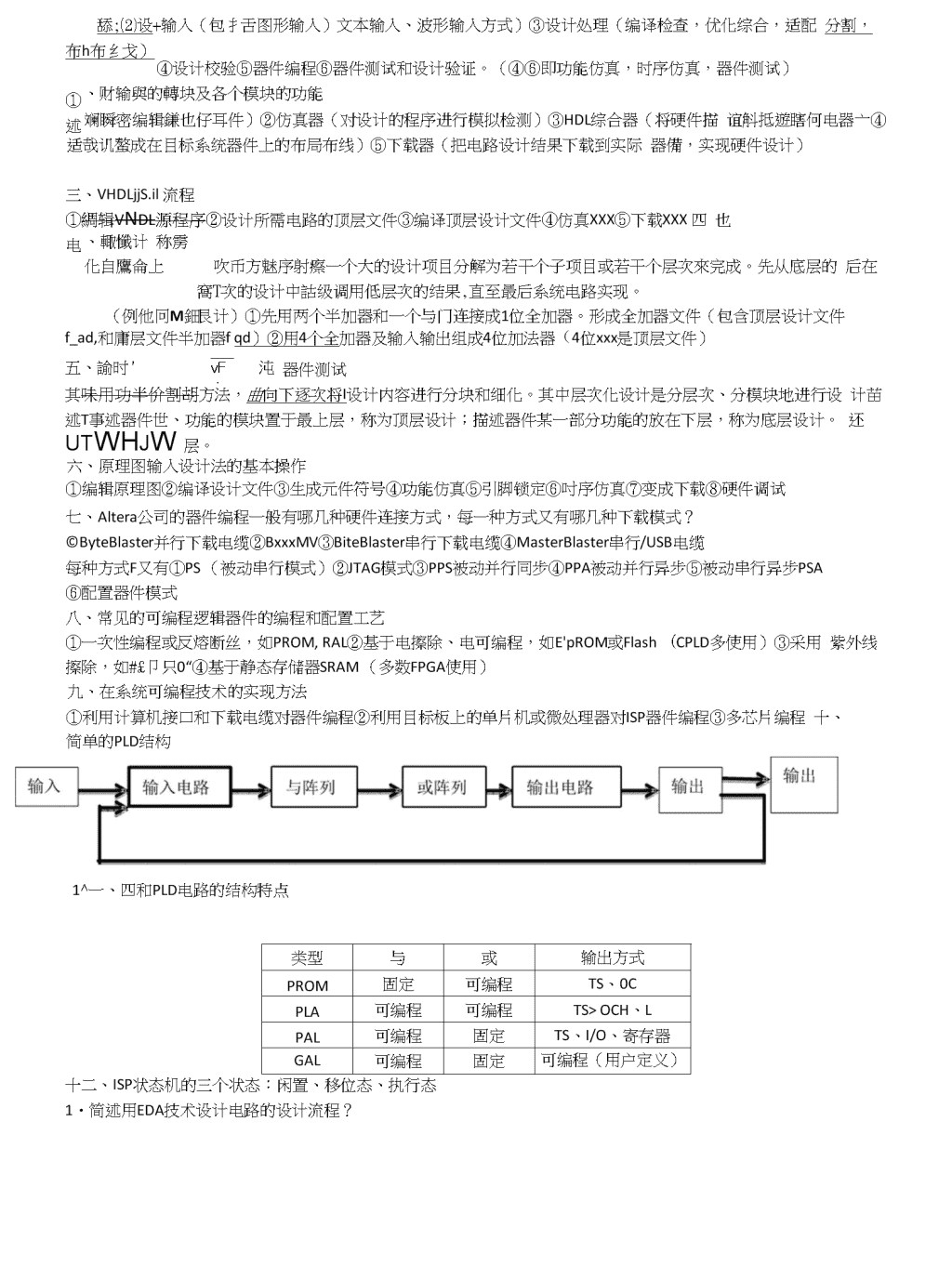

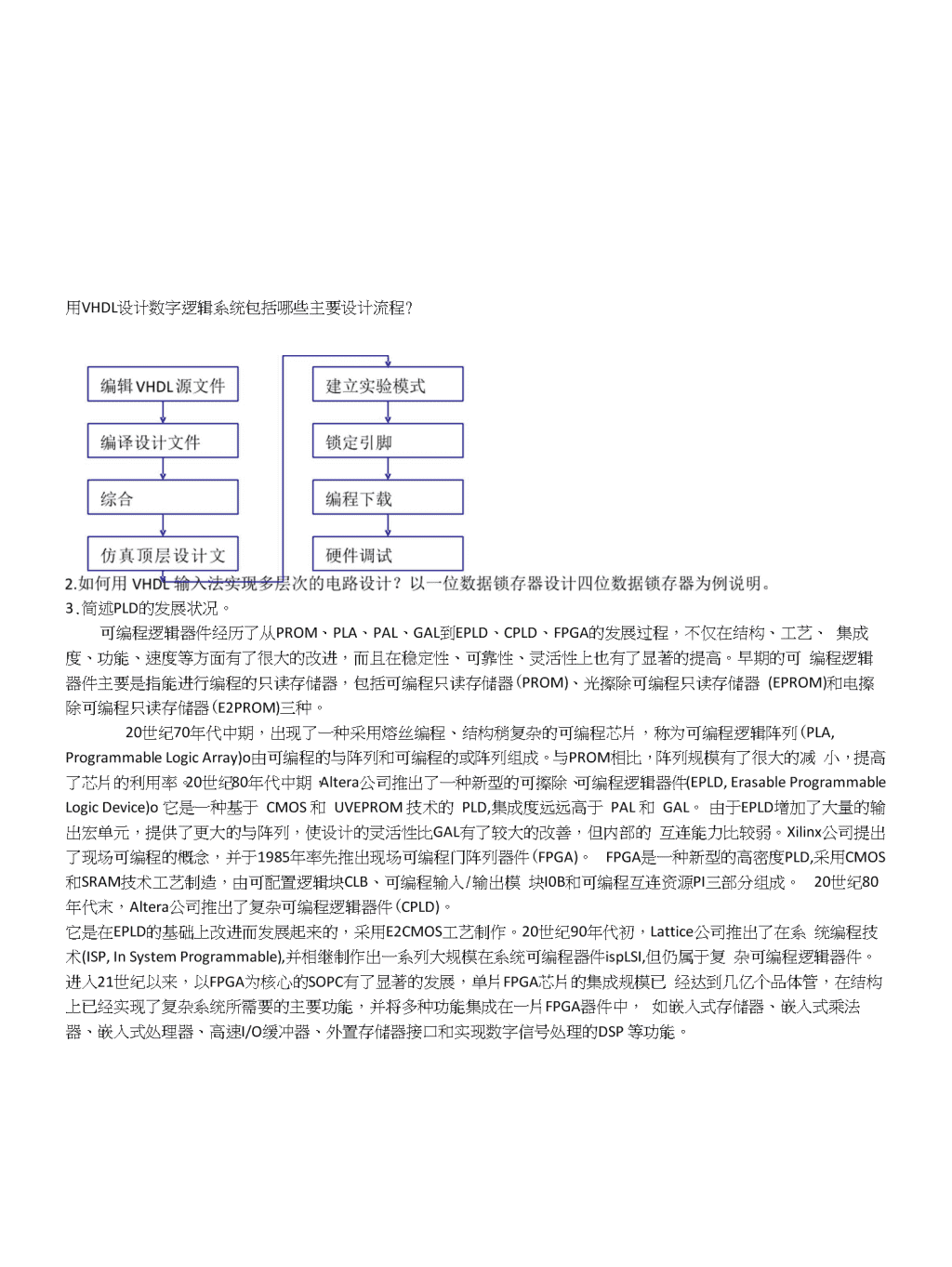

舔;⑵设+输入(包扌舌图形输入)文本输入、波形输入方式)③设计处理(编译检查,优化综合,适配分割,布h布纟戈)①述④设计校验⑤器件编程⑥器件测试和设计验证。(④⑥即功能仿真,时序仿真,器件测试)、财输與的轉块及各个模块的功能斓瞬密编辑鎌也仔耳件)②仿真器(对设计的程序进行模拟检测)③HDL综合器(将硬件描谊斛抵遊瞎何电器亠④适哉讥螯成在目标系统器件上的布局布线)⑤下载器(把电路设计结果下载到实际器備,实现硬件设计)三、VHDLjjS.il流程①綢辑vNdl源程序②设计所需电路的顶层文件③编译顶层设计文件④仿真XXX⑤下载XXX四也电、輙懺计称雳化自鷹侖上(例他冋M鈿吹币方魅序射瘵一个大的设计项目分解为若干个子项目或若干个层次來完成。先从底层的后在窩T次的设计中詁级调用低层次的结果,直至最后系统电路实现。艮计)①先用两个半加器和一个与门连接成1位全加器。形成全加器文件(包含顶层设计文件f_ad,和庸层文件半加器fqd)②用4个全加器及输入输出组成4位加法器(4位xxx是顶层文件)vF:五、諭时'沌其味用功半价割胡方法,曲向下逐次将I设计内容进行分块和细化。其中层次化设计是分层次、分模块地进行设计苗述T事述器件世、功能的模块置于最上层,称为顶层设计;描述器件某一部分功能的放在下层,称为底层设计。还utWHjW层。器件测试六、原理图输入设计法的基本操作①编辑原理图②编译设计文件③生成元件符号④功能仿真⑤引脚锁定⑥吋序仿真⑦变成下载⑧硬件调试七、Altera公司的器件编程一般有哪几种硬件连接方式,每一种方式又有哪几种下载模式?©ByteBlaster并行下载电缆②BxxxMV③BiteBlaster串行下载电缆④MasterBlaster串行/USB电缆每种方式F又有①PS(被动串行模式)②JTAG模式③PPS被动并行同步④PPA被动并行异步⑤被动串行异步PSA⑥配置器件模式八、常见的可编程逻辑器件的编程和配置工艺①一次性编程或反熔断丝,如PROM,RAL②基于电擦除、电可编程,如E'pROM或Flash(CPLD多使用)③采用紫外线擦除,如#£卩只0“④基于静态存储器SRAM(多数FPGA使用)九、在系统可编程技术的实现方法①利用计算机接口和下载电缆对器件编程②利用目标板上的单片机或微处理器对ISP器件编程③多芯片编程十、简单的PLD结构1^一、四和PLD电路的结构特点类型与或输出方式PROM固定可编程TS、0CPLA可编程可编程TS>OCH、LPAL可编程固定TS、I/O、寄存器GAL可编程固定可编程(用户定义)十二、ISP状态机的三个状态:闲置、移位态、执行态1・简述用EDA技术设计电路的设计流程?\n用VHDL设计数字逻辑系统包括哪些主要设计流程?3.简述PLD的发展状况。可编程逻辑器件经历了从PROM、PLA、PAL、GAL到EPLD、CPLD、FPGA的发展过程,不仅在结构、工艺、集成度、功能、速度等方面有了很大的改进,而且在稳定性、可靠性、灵活性上也有了显著的提高。早期的可编程逻辑器件主要是指能进行编程的只读存储器,包括可编程只读存储器(PROM)、光擦除可编程只读存储器(EPROM)和电擦除可编程只读存储器(E2PROM)三种。20世纪70年代中期,出现了一种采用熔丝编程、结构稍复杂的可编程芯片,称为可编程逻辑阵列(PLA,ProgrammableLogicArray)o由可编程的与阵列和可编程的或阵列组成。与PROM相比,阵列规模有了很大的减小,提高了芯片的利用率。20世纪80年代中期,Altera公司推出了一种新型的可擦除、可编程逻辑器件(EPLD,ErasableProgrammableLogicDevice)o它是一种基于CMOS和UVEPROM技术的PLD,集成度远远高于PAL和GAL。由于EPLD增加了大量的输出宏单元,提供了更大的与阵列,使设计的灵活性比GAL有了较大的改善,但内部的互连能力比较弱。Xilinx公司提出了现场可编程的概念,并于1985年率先推出现场可编程门阵列器件(FPGA)。FPGA是一种新型的高密度PLD,采用CMOS和SRAM技术工艺制造,由可配置逻辑块CLB、可编程输入/输出模块I0B和可编程互连资源PI三部分组成。20世纪80年代末,Altera公司推出了复杂可编程逻辑器件(CPLD)。它是在EPLD的基础上改进而发展起来的,采用E2CMOS工艺制作。20世纪90年代初,Lattice公司推出了在系统编程技术(ISP,InSystemProgrammable),并相继制作出一系列大规模在系统可编程器件ispLSI,但仍属于复杂可编程逻辑器件。进入21世纪以来,以FPGA为核心的SOPC有了显著的发展,单片FPGA芯片的集成规模已经达到几亿个品体管,在结构上已经实现了复杂系统所需要的主要功能,并将多种功能集成在一片FPGA器件中,如嵌入式存储器、嵌入式乘法器、嵌入式处理器、高速I/O缓冲器、外置存储器接口和实现数字信号处理的DSP等功能。\n4•简述简单的PLD的基本结构PLD可分为三块结构:宏单元(Marocell),可编程连线(PIA)和I/O控制块。宏单元是PLD的基本结构,由它来实现基本的逻辑功能。可编程连线负责信号传递,连接所有的宏单元。I/O控制块负责输入输出的电气特性控制,比如可以设定集电极开路输出,摆率控制,三态输出等。5.以MAX7000A为例,简述EPLD和CPLD的基本结构MAX7000在Altera公司生产的CPLD中是速度最快的一个系列,包扌舌MAX7000E、MAX7000S、MAX7000A三种器件,集成度为600〜5000个可用门、32〜256个宏单元和36〜155个可用I/O引脚。EPLD和CPLD的基本结构1可编程逻辑宏单元逻辑宏单元内部主要包括与或阵列、可编程触发器和多路选择器等电路,能独立地配置为时序或组合工作方式。EPLD器件与GAL器件相似,其逻辑宏单元与I/O做在一起,称为输岀逻辑宏单元,但其宏单元及与阵列数FI比GAL大得多。CPLD器件的宏单元在内部,称为内部逻辑宏单元。2可编程I/O单元输入/输出单元简称I/O单元(或I0C),它是内部信号到I/O引脚的接口部分。由于阵列型HDPLD通常只有少数几个专用输入端,大部分端口均为I/O端,而且系统的输入信号常常需要锁存,因此I/O常作为一个独立单元來处理。3可编程连线阵列可编程连线阵列的作用是在各逻辑宏单元之间以及逻辑宏单元和I/O单元Z间提供互连网络。各逻辑宏单元通过可编程连线阵列接收来自专用输入或输入端的信号,并将宏单元的信号反馈到其需要到达的日的地。这种互连机制有很大的灵活性,它允许在不影响引脚分配的情况下改变内部的设计。6.简述Altera公司的产品以及其特点Altera提供的CPLD和FPGA。在1988年推出MAX®CPLD产品系列,为了应对当今更为复杂的系统需求,Altera推出高密度的Stratix®IIFPGA系列、低成本的Cyclone™FPGA、MAxIICPLD系列、以及带有内嵌接收器的StratixGX系列。AlteraAltera最新版Quartus®TI设计软件易于使用,具有面向团队的设计流程,能够与第三方软件包无缝协同工作,提供系统级设计流程访问,极大的降低了整体开发时间。QuartusII软件是业内设计CPU)、FPGA和结构化ASIC功能最强大的软件。7.简述FLEX10K的级联链实现多输入的逻辑功能原理级联链采用与逻辑或者利用摩根反演率获得的或逻辑连接相邻LE的输出,如图0-11所示。级联链可以在最小延时的情况下构成多输入逻辑函数,实现高速多信号扇入(Fan-In)功能。当柑邻的LUT同时并行完成函数运算时,级联链可以串接各LUT运算的中间信号。每增加1个LE,函数的输入变蜀可以增加4个,但信号延时大约增加0.7ns。当级联链多于8级时,也采用半长线构成长级联链在行间跳就交狀接LAB。同长进位链一样,每彳亍的长级联链也有…对,各被EAB分为两段。级联链串接相邻LE形成的多扇入结构如图(Ml\n所示。〃个LE通过与逻辑级联或者或逻辑级联可以实现4/;个变量的逻轲函数.LE的延时约1.6ps,级联链延时约0-7抄,实现•个〃级级联逻轲因数的总延迟时间约为1-6+0.7〃(“)。山3』|叫741(4//—I>..<4rr—-h|d[3JJ|训7」]叫(4”一I〉(4rr—4)Jlb)理越尙级双琏閉0-11级朕进形成的事削入结构QuartusII的编译器▲进行设计处理时会为一般逻辑功能块或1pm参数化逻辑功能块门幼生成进位链或级联琏•设计者也可4设汁输入期间进行人匸干预。\n编稈题:①锁存器LIBRARYIEEE;USELIBRARYIEEE.STD_LOGIC_1164.ALL;ENTILYIatchlISPORTfd:INSTD_L0GIC;ena:INSTD_L0GIC;q:0UTSTD_L0GIC);ENDlatchl;ARCHITECTUREoneOFlatchlISBEGINPROCESS(d,ena)BEGINIFena^rTHENq<=d;ENDIF;ENDPROCESS;ENDone;②4选1数据选择器LIBRARYIEEE;USELIBRARYIEEE.STDLOGIC1164.ALL;ENTILYmux41ISPORT(si,s2:INSTD_LOGIC;a,b,c,d:INSTD_LOGIC;z:OUTSTD_LOGIC);ENDmux41;ARCHITECTUREexample7OFmux41ISSIGNALs:STD_LOGIC_VECTOR(lD0WNT00);BEGINs<=sl&s2CASEsISWHEN//00,,=>z<=a;WHENZ/Olw=>z<=b;WHEN//10,,=>z<=c;WHEN//ll,,=>z<=d;WHENOTHERS二〉zv二'X';ENDCASE;ENDPROCESS;ENDexample7;③8位奇偶校验器的描述LIBRARYIEEE;USELIBRARYIEEE.STDLOGIC1164.ALL;ENTITYp_checkISPORT(a:INSTD_L0GIC_VECT0R(7DOWNTO0);y:OUTSTD_LOGIC);ENDp_check;ATCHITECTUREexample8OFp_checkISBEGINPROCESS(a)VARIABLEtemp:STD_LOGIC;BEGINTemp:二'O';FORnINOTO7LOOP;temp:=tempXORa(n);ENDLOOPY<=temp;ENDPROCESS;ENDexample8;④8线・3线优先编码器的设计LIBRARYIEEE;USELIBRARYIEEE.STDLOGIC1164.ALL;ENTITYcoderISPORT(a:INSTD_L0GIC_VECT0R(7DOWNTO0);y:OUTSTD_L0GIC_VECT0R(2DOWNTO0);ENDcoder;ATCHITECTUREexample6OFcoderISBEGINIF(a(7)=0,)THENy<=wlll//;ELSIF(a(6)=0,)THENy<=w110,z;ELSIF(a(5)=0,)THENy<=,,101,/;ELSIF(a(4)=0,)THENyv=T00";ELSIF(a(3)=©)THENy<=,,011,/;ELSIF(a(2)=/0,)THENyV010";ELSIF(a⑴二'0')THENy<=,001,/;ELSIF(a(0)=O7)THENyv二〃000";ELSEyv二〃000";ENDPROCESS;ENDexample6;⑤半加器LIBRARYIEEE;USELIBRARYIEEE.STD_LOGIC_1164.ALL;ENTITYh_adderISPORT)a,b:INSTD_LOGIC;so,co:OUTSTD_LOGIC);ENDhadder;ATCHITECTUREexample2OFh_adderISBEGINso<=aXORb;co<=aANDb;ENDexample2;@2选1数据选择器LIBRARYIEEE;USELIBRARYIEEE.STDLOGIC1164.ALL;ENTILYmux21ISPORT(a,b:INSTD_LOGIC;s:INSTD_LOGIC;y:OUTSTD_LOGIC);ENDmux21;ATCHITECTUREexample3OFmux21ISBEGINy<=aWHENs=0?ELSEb;ENDexample3;⑧求最大值的函数LIBRARYIEEE;USELIBRARYIEEE.STD_LOGIC_1164.ALL;PACKAGEbpacISFUNCTIONmax(a,b:INSTD_LOGIC_VECTOR)RETURNSTD_LOGIC_VECTOR;END;PACKAGEBODYbpacISFUNCTIONmax(a,b:INSTD_LOGIC_VECTOR)RETURNSTD_LOGIC_VECTORISBEGINIF(a>b)THENRETURNa;ELSERETURNb;ENDIF;ENDmax;END;18.8位乘法器LIBRARYIEEE;USEIEEE.STDLOGIC1164.ALL;ENTITYmulISPORT(a,b:INintegerrange0to255;q:OUTintegerrange0to65536);ENDmul;ARCHITECTUREoneOFmulISBEGINq<=a*b;ENDone;⑦异步清除十进制加法计数器LIBRARYIEEE;USELIBRARYIEEE.STD_LOGIC_1164.ALL;\nENTILYcntlOyISPORT(clr:INSTD_LOGIC;clk:INSTD_LOGIC;ent:BUFFERINTERGERRANGE9DOWNTO0);ENDcntlOy;ATCHITECTUREexample9OFcntlOyISBEGINPROCESS(clr,clk)BEGINIFclr=O,THENcnt<=,0,;ELSIFclk'EVENTANDelk=TTHENIF(cnt=9)THENcntv=O;ELSEcnt<=cnt+1;ENDIF;ENDIF;ENDPROCESS;ENDexample9;⑩编辑4位二进制计数器LIBRARYIEEE;USELIBRARYIEEE.STDLOGIC1164.ALL;ENTITYcnt4eISPORT(clk,ena:INSTD_LOGIC;cout:OUTSTD_LOGIC;q:BUFFERINTEGERRANGE0TO15);ENDcnt4e;ARCHITECTUREoneOFcnt4eISBEGINPROCESS(clk,ena)BEGINIFclk'EVENTANDelk"THENIFcIk'l'THENIFq=15THENq<=0;coutv二'O';ELSIFq=14THENq<=q+l;coutv二T;ELSEq<=q+l;ENDIF;ENDIF;ENDIF;ENDPROCESS;ENDone;⑨利用2输入端与非门元件,设计4输入端的与非一与非电路第一步:设计2输入端与非门:LIBRARYIEEE;USELIBRARYIEEE.STD_LOGIC_1164.ALL;ENTITYnd2ISPORT)azb:INSTD_LOGIC;c:OUTSTD_LOGIC);ENDnd2;ARCHITECTUREnd2behvOFnd2ISBEGINc<=aNANDb;ENDnd2behv;第二步:将设计的元件声明装入my_pkg程序包中,包含2输入端与非门元件的my_pkg程序包的VHDL源程序:LIBRARYIEEE;USELIBRARYIEEE.STD_LOGIC_1164.ALL;PACKAGEmy_pkgISComporientnd2PORT(a,b:INSTD_LOGIC;c:OUTSTD_LOGIC);ENDComponent;ENDmy_pkg;第三步:一用元件例化产生图所示电路:LIBRARYIEEE;USELIBRARYIEEE.STDLOGIC1164.ALL;USEwork.my_pkg.ALL;ENTITYord41ISPORT(al,bl,clzdl:INSTD_LOGIC;zl:OUTSTD_LOGIC);ENDord41;ARCHITECTUREord41behvOFord41ISSIGNALx,y:STD_LOGIC;BEGINul:nd2PORTMAP(al,bl,x);u2:nd2PORTMAP(a=>cl,b=>dl,c=>y);u3:nd2PORTMAP(x,y,c=>zl);ENDord41behv;15.8位一进制数据比较器LIBRARYIEEE;USEIEEE.STDLOGIC1164.ALL;ENTITYcomp8ISPORT(a,b:INSTD_LOGIC_VECTOR(7DOWNTO0);fa,fb,fe:OUTSTD_LOGIC);ENDcomp8;ARCHITECTUREoneOFcomp8ISBEGINPROCESS(a,b)BEGINIFa>bTHENfa<='l';fb<=,0';fe<='0';ELSIFaS<=B”0000”;WHEN=>S<=B"0001";WHEN=>S<=B"0010";WHENB,,11100111n=>S<=B"0011M;WHEN=>S<=B"0100";WHEN=>S<=B"0101H;WHEN=>S<=B"0110";WHEN6"11010111,'=>S<=B'^lll";WHEN=>S<=B"1000H;WHEN=>S<=B"1001";WHEN=>S<=B"1010";WHEN=>S<=B"1011";WHEN=>S<=B"1100H;WHEN=>S<=B"1101H;WHENB"01111011n=>S<=BH1110M;WHENB'^lllOlir=>S<=B"llll";WHENOTHERS=>S<=Bn0000";ENDCASE;ENDPROCESS;ENDstruc;19.4位锁存器4位锁存器ENTITYREG4BISPORT(LOAD:INSTD_LOGIC;DIN:INSTD_L0GIC_VECT0R(3DOWNTO0);DOUT:OUTSTD_L0GIC_VECT0R(3DOWNTO0));ENDREG4B;ARCHITECTUREoneOFREG4BISBEGINPROCESS(LOAD,DIN)BEGINIFLOAD'EVENTANDLOAD二TTHENDOUT<=DINENDIF;ENDPROCESS;ENDone;議A口辆经现丫二础+be十QC12•编辑七段显示器LIBRARYIEEE;USEIEEE.STDLOGIC1164.ALL;ENTITYDEC7sISPORT(a:INBIT_VECTOR(3DOWNTO0);Ied7s:OUTBIT_VECTOR(7DOWNTO0));END;ARCHITECTUREoneOFDec7sISBEGINPROCESS(A)BEGINCASEA(3DOWNTO0)ISWHEN"0000"=>LED7s<=,,00111111";WHEN,,0001"=>LED7s<=,,00000110";WHEN,,0010,,=>LED7s<=,,01011011";WHEN"0011,,=>LED7s<=,,01001111";WHEN,,0100,,=>LED7s<="01100110";WHEN,,0101,,=>LED7s<="01101101";WHEN,,0110,,=>LED7s<=,,01111101,';WHEN,,0111,,=>LED7s<=,,00000111";WHEN,,1000,,=>LED7s<="01111111";WHEN•,1001"=>1£075<="01101111,';WHEN,,1010,,=>LED7s<=,,01110111";WHEN',1011,,=>LED7s<=,,01111100";WHEN"1100"=>LED7s<="00111001";WHEN,,1101"=>1£075<=,,01011110,';WHEN,,1110,,=>LED7s<=,,01111001";WHEN•,llll"=>LED7s<=,,01110001";WHENOTHERS=>NULL;ENDCASE;ENDPROCESS;ENDone;13.3线・8线译码器的设计LIBRARYIEEE;USEIEEE.STDLOGIC1164.ALL;ENTITYdecoderISPORT(a,b,c,ena:INBIT;y:OUTBIT_VECTOR(7DOWNTO0));ENDdecoder;ARCHITECTUREoneOFdecoderISBEGINPROCESS(a,b,c,ena)VARIABLEcba:BIT_VECTOR(2DOWNTO0);BEGINcba:二(c&b&a);IF(ena='l')THENy<="11111111";ELSECASE(cba)ISWHEN”000”=>y<=WHEN"001"=>y<=WHEN”010”=>y<=,,11111011u;WHEN=>y<=WHEN“100”=>y<="11101111";WHEN"101"=>y<=WHEN"110"=>y<="10111111";WHEN"111"=>y<="01111111";WHENOTHERS=>NULL;ENDCASE;ENDIF;ENDPROCESS;ENDone;16.ROM的设计LIBRARYIEEE;USEIEEE.STDLOGIC1164.ALL;\nENTITYfrom_romISPORT(clk,cs:INSTD_LOGIC;■-addr:ININTEGERRANGE0TO7;q:OUTSTD_LOGIC_VECTOR(7DOWNTO0));ENDENTITYfrom_rom;ARCHITECTUREoneOFfrom_romISTYPErom_typeISARRAY(0TO刀OFSTD_LOGIC_VECTOR(7DOWNTO0);BEGINPROCESS(clk,addr,cs)ISVARIABLEmem:rom_type;BEGINmem(0):=“01000001”;mem⑴U'OIOOOOIO”;mem(2):=,,01000011,,;mem(3):=,,01000100,';mem(4):=”01000:10:L”;mem(5):=”010001K)”;mem(6):="01000111,,;mem(7):=,,01001000n;IFcIk'eventANDclk=*rTHENq<=(others=>'Z');IFcs=,O,THENq<=mem(addr);ENDIF;ENDIF;ENDPROCESS;ENDone;17.JK触发器的设计LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYmyjkffISPORT(j,k,clr:INSTD_LOGIC;elk:INSTD_LOGIC;qzqn:BUFFERSTD_LOGIC);ENDmyjkff;ARCHITECTUREoneOFmyjkffISBEGINPROCESS(j,k,clr,clk)VARIABLEjk:STD_LOGIC_VECTOR(lDOWNTO0);BEGINjk:=(j&k);IFclr=,O,THENq<='O';qn<='1';ELSIFclk'EVENTANDelk='O'THENP0RT(sl,s2:IN_STD_L0GIC;a,bzc,d:IN_STD_LOGIC;Z:OUTSTD_LOGIC;ENDmux41;ARCHITECTUREexample7OFmux41ISSIGNAMs:STD_LOGIC_VECTOR(lDOWNTO0);BEGINs<=sl&s2;PR0CESS(sl,s2,a,b,c,d)BEGINCASEsISWHENnOO"=>z<=a;WHEN"01,,=>z<=b;WHEN"10"=>z<=c;WHEN"ll,,=>z<=d;WHENOTHERS二〉zv二X;ENDCASE;ENDPROCESS;ENDexample;21.-三态输出8D锁存器LIBRARYIEEE;ENTITYIatch8ISPORT(clr,clkena,oe:INSTD_LOGIC;d:INSTD_L0GIC_VECT0R(7DOWNTO0);q:BUFFERSTD_L0GIC_VECT0R(7DOWNTO0));ENDIatch8;ARCHITECTOREoneOFIatch8ISSIGNALq_temp:STD_L0GIC_VECT0R(7DOWNTO0);BEGNIul:PROCESS(clk,clr,ena,oe)BEGINIFelk='O'THENq_temp<="00000000";ELSIFclk'EVENTANDelk='1*THENIF(ena=l)THENq_temp<=d;ENDIF;ENDIF;IFoe='1'THENq<='zzzzzzzz”;ELSEq<=q_temp;ENDIF;ENDPROCESSul;ENDone;CASEjkISWHEN“00”=>q<=q;qnuqn;WHEN"01n=>q<=*O';qn<='1';WHEN"10n=>q<=l;qnv二'O';WHEN"ll"=>q<=NOTq;qnNOTqn;WHENOTHERS=>NULL;ENDCASE;ENDIF;ENDPROCESS;ENDone;7.20.用VHDL设计一个四选一的数据锁存器LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYmux41IS14.16选1数据选择器的设计LIBRARYIEEE;USEIEEE.STDLOGIC1164.ALL;ENTITYmuxl6_lISPORT(sO,sl,s乙s3疋na:INSTD_LOGIC;\na:INSTD_L0GIC_VECT0R(15DOWNTO0);y:OUTSTD_LOGIC);ENDmuxl6_l;ARCHITECTUREoneOFmuxl6_lISSIGNALs:STD_L0GIC_VECT0R(3DOWNTO0);BEGINs<=s0&sl&s2&s3;PROCESS(sO,sl,s2,s3,ena)BEGINIFena二TTHENyv二'O';ELSECASEsISWHEN"0000"=>y<=a(0);WHEN”0001”=>y<=a(l);WHEN"0010"=>y<=a(2);WHEN"OOll"=>y<=a(3);WHEN"0100"=>y<=a(4);WHEN"0101"=>y<=a(5);WHEN"0110"=>y<=a(6);WHEN"0111"=>y<=a⑺;WHEN"1000"=>y<=a(8);WHEN"lOOl"=>y<=a(9);WHENH1010"=>y<=a(10);WHEN"1011"=>y<=a(ll);WHEN"1100"=>y<=a(12);WHEN"1101"=>y<=a(13);WHEN"1110"=>y<=a(14);WHEN"1111"=>y<=a(15);WHENOTHERS=>y<='X';ENDCASE;ENDIF;ENDPROCESS;ENDone;