- 483.79 KB

- 2022-07-30 发布

- 1、本文档由用户上传,淘文库整理发布,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,请立即联系网站客服。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细阅读内容确认后进行付费下载。

- 网站客服QQ:403074932

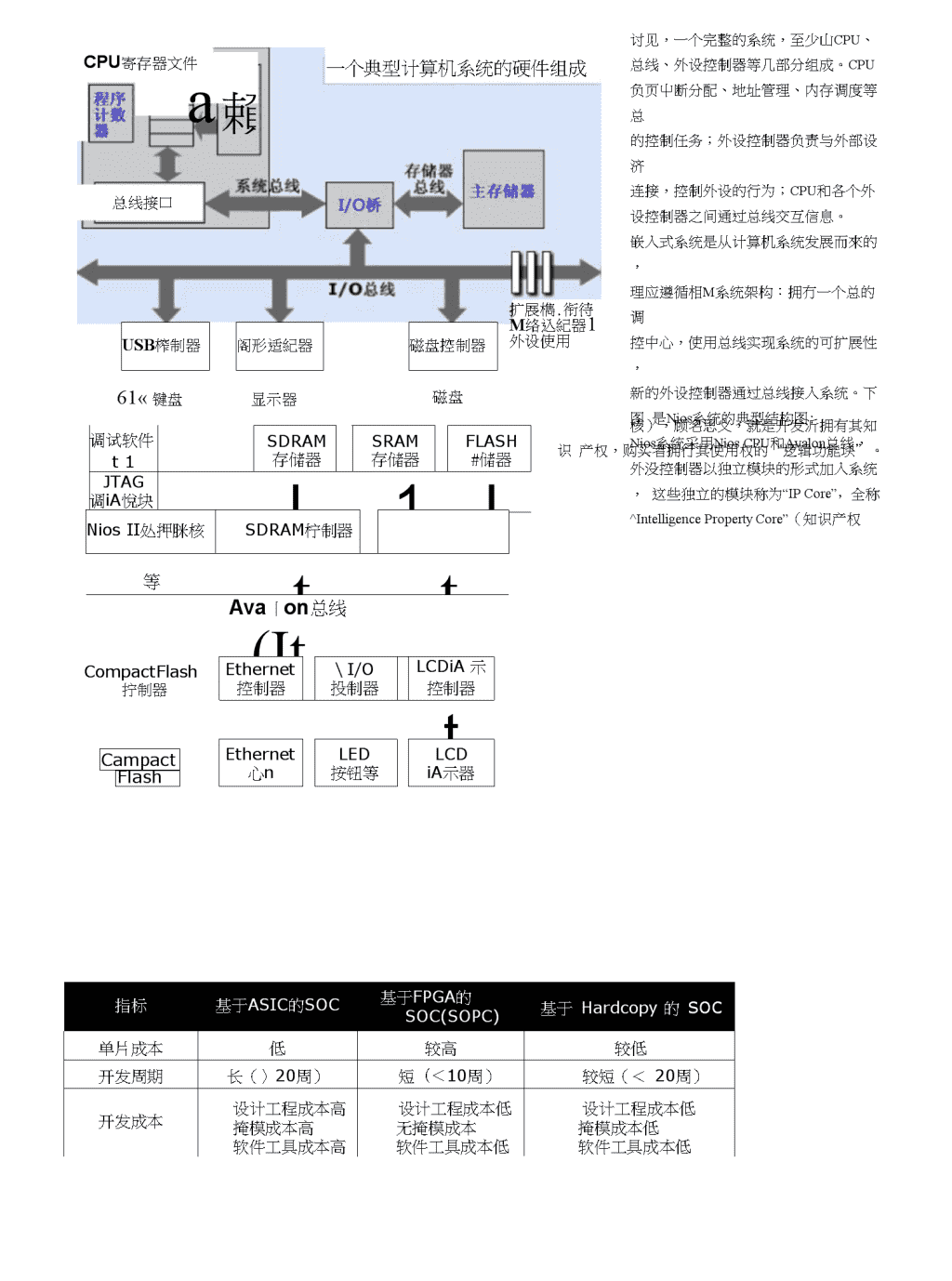

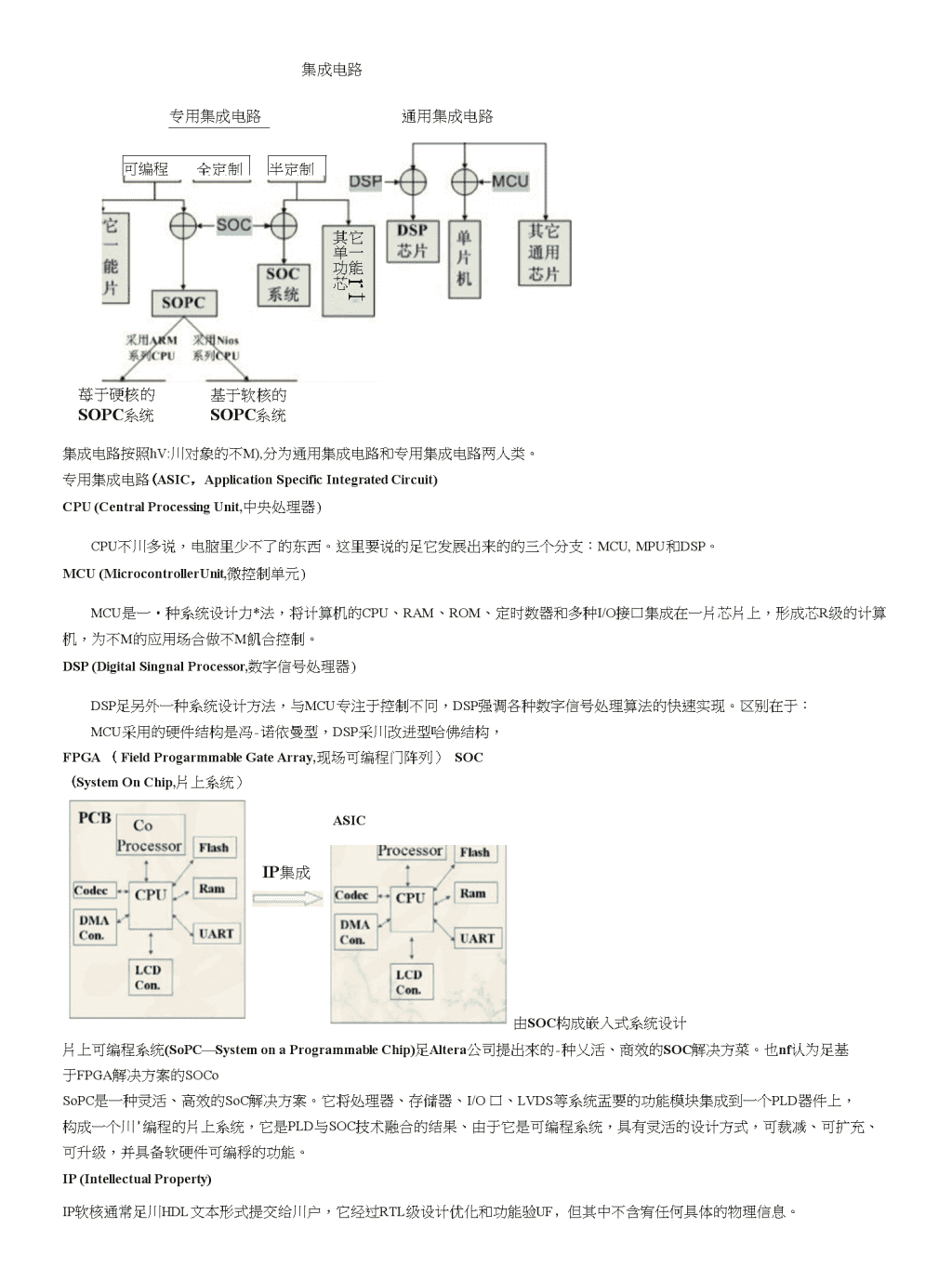

CPU寄存器文件扩展檇.衔待M络込紀器1外设使用总线接口一个典型计算机系统的硬件组成賴aUSB榨制器阁形适紀器磁盘控制器磁盘讨见,一个完整的系统,至少山CPU、总线、外设控制器等几部分组成。CPU负页屮断分配、地址管理、内存调度等总的控制任务;外设控制器负责与外部设济连接,控制外设的行为;CPU和各个外设控制器之间通过总线交互信息。嵌入式系统是从计算机系统发展而來的,理应遵循相M系统架构:拥冇一个总的调控中心,使用总线实现系统的可扩展性,新的外设控制器通过总线接入系统。下图是Nios系统的典型结构图:Nios系统采用NiosCPU和Avalon总线,外没控制器以独立模块的形式加入系统,这些独立的模块称为“IPCore”,全称^IntelligencePropertyCore”(知识产权调试软件t1SDRAM存储器SRAM存储器FLASH#储器JTAG调iA悅块I1I61«键盘显示器核),顾名思义,就是开发沂拥有其知识产权,购买者拥行其使用权的“逻辑功能块”。NiosII处押脒核SDRAM柠制器等ttCampactFlashAva丨on总线(ItemetlIliillil/OLCDiuEthernet控制器\I/O投制器LCDiA示控制器tEthernetLEDLCD心n按钮等iA示器CompactFlash拧制器指标基于ASIC的SOC基于FPGA的SOC(SOPC)基于Hardcopy的soc单片成本低较高较低开发周期长(〉20周)短(<10周)较短(<20周)开发成本设计工程成本高掩模成本高软件工具成本高设计工程成本低无掩模成本软件工具成本低设计工程成本低掩模成本低软件工具成本低\n一次投片情况一次投片成功率低,成本高,耗时长可现场配置一次投片成功率近100%,成本低,耗时短集成技术0.25um~90nm0.25um^90nm0.25um^90nm可重构性不可重构可重构不可重构\n集成电路专用集成电路可编程全定制半定制基于软核的SOPC系统苺于硬核的SOPC系统它一能rf其单功芯通用集成电路集成电路按照hV:川对象的不M),分为通用集成电路和专用集成电路两人类。专用集成电路(ASIC,ApplicationSpecificIntegratedCircuit)CPU(CentralProcessingUnit,中央处理器)CPU不川多说,电脑里少不了的东西。这里要说的足它发展出来的的三个分支:MCU,MPU和DSP。MCU(MicrocontrollerUnit,微控制单元)MCU是一•种系统设计力*法,将计算机的CPU、RAM、ROM、定时数器和多种I/O接口集成在一片芯片上,形成芯R级的计算机,为不M的应用场合做不M飢合控制。DSP(DigitalSingnalProcessor,数字信号处理器)DSP足另外一种系统设计方法,与MCU专注于控制不冋,DSP强调各种数字信号处理算法的快速实现。区别在于:MCU采用的硬件结构是冯-诺依曼型,DSP采川改进型哈佛结构,FPGA(FieldProgarmmableGateArray,现场可编程门阵列)SOC(SystemOnChip,片上系统)IP集成ASIC由SOC构成嵌入式系统设计片上可编程系统(SoPC—SystemonaProgrammableChip)足Altera公司提出來的-种乂活、商效的SOC解决方菜。也nf认为足基于FPGA解决方案的SOCoSoPC是一种灵活、高效的SoC解决方案。它将处理器、存储器、I/O口、LVDS等系统盂要的功能模块集成到一个PLD器件上,构成一个川'编程的片上系统,它是PLD与SOC技术融合的结果、由于它是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件可编稃的功能。IP(IntellectualProperty)IP软核通常足川HDL文本形式提交给川户,它经过RTL级设计优化和功能验UF,但其中不含宥任何具体的物理信息。\nIP硬核是基于半导体C艺的物理设计,己有固定的拓扑布局和具体工艺,并己经过工艺验证,具有讨保证的性能基于嵌入IP硬核的SOPC系统有以下的缺点:1.器件价格相对偏髙。2.山于硬核圮预先梢入的,设计沂无法根据实际盂要改变处理器的结构。3.无法根据实际需要在同一FPGA屮使用多个处理器核。4.无法裁剪处珂器的硬件资源以降低FPGA成本。5.只能在特定的FPGA中使用硬核。NiosII的特点:最大处理性能提高了3倍CPU内核面积最大可缩小1/232位RISC嵌入式处理器具有超过200DMIP的性能,在低成本FPGA中实现成本只有35美分。由于NiosII是软核形式,其可在多种系统设置组合中进行选择,满足成本和功能要求。可延长产品生命周期,防止出现处理器逐渐过时的情况。NiosII处理器系列包括三种内核快速:性能最髙,但占用的逻辑资源最多。经济:占用的逻辑资源最少,但性能最低标准:平衡的性能和尺寸。叫0811^内核比第一代的抑08€?11更快,占用的资源更少。NiosII系列处理器支持多达256条的定制指令,加速通常由软件实现的逻辑和k杂数学算法。在采用NIOSII处理器设计嵌入式系统时,一般遵循如下的流程:1.分析系统需求说明,包括功能盂求和性能要求等;2.建立QuartusII工程,建立顶层实体;3.调用SOPCBuilder•:成•-个用户定制的系统模块(毡括NIOSII及标准外没模块);4.将SOPC系统模块集成到硬件工程中,并添加一些模块,可以足Altera公司提供的LPM模块、第三提供的或用户自己定制的模块:5.在顶层实体屮,将SOPC系统模块、Altera的LPM或川户自定义的模块连接起來;6.分配引脚和编译丁程,编译生成系统的硬件配背文件.sof和.pof文件:7.K载工程,验证,将配置文件下载到开发板上进行验证;8.软件开发,开发可以使用IDE开发环境,也可以使用SDKShell:9.编译软件工程,生成可执行文件.elf;10.调试程序,将硬件配■文件下载到开发板,将可执行文件下载到RAM,直到软硬件协同工作。可配置嵌入式软核处理器的优势1.提供合理的性能组合2.提升系统的性能3.降低系统成本4.延长产品的生命周期SOPC设汁包括以NiosII软核处理器为核心的嵌入式系统的硬件配置、硬件设计、硬件仿真、IDE环境的软件设汁、软件调试等软件开发软件开发使用NiosIIIDE,它是一个基于EclipseIDE架构的集成开发环境,它包括:GNU开发丁具(标准GCC编译器,连接器,汇编器和makefile工具等);蕋于GDB的调试器,包括软件仿真和硬件调试;提供用户一个硬件抽象层HAL;提供嵌入式操作系统MicroC/OS-n和LwTCP/IP协议栈的支持:提供帮助用户快速入门的软件模板;捉供FlashF载支持(FlashProgrmmer和QuartusIIProgrammer)■NiosTT是一种软核(Soft-Core)处理所诮软核,是指未被固化在砘片上,使用吋需耍借助RDA软件对其进行配置并下载到可编程芯片(比如FPGA)中的TP核。软核最大的特点就是可由用户按需要进行配置。NiosII的寄存器文件包括32个通川寄存器和6个控制寄存器,NiosII结构允许将來添加浮点奇存器种类描述\n算水运算ALU支持有符号和无符号数的加、减、乘和除法关系运»支持有符号和无符号数的等于、不等于、大于等于和小于(==,!=>=,<)关系运算逻辑运算支持AND、OR、NOR和XOR逻辑运算移位运兑支持移位和循环移位运算,4:甸条指令屮川'以将数据移位和环移0到31位。支持算术右移和算术左移,还支持左、右循坏移位\n■NiosII处理器支特W个复位信号:reset和cpu_resetrequest■reset:是一个强制处理器核立即进入复位状态的全局硬件复位倍号。■cpu_resetrequest:是-个可以让CPU鼓位似不影响NiosII系统外没的W部超位信1CPU位后,NiosII处理器将执行下列操作:淸除状态寄存器status,使之为0x0;指令Cache与程序存储器的关联被置为无效,处理器从阆态程序存储器(比如Flash)屮的reset地址处取得笫一条指令;从复位地址处开始执行程序。NiosII运行模式3种:用户棋式(UserMode);超级用户模式(Supervisor);调试揽^(Debug)通常系统程序代码运行在超级用户模式为32位宽度。指令集提供字节,半字(16bit)或字(32位)的读写指令。NiosII结构采用小端模:A:,对于保存在存储器中的人丁8位的映射到的具体位S在生成系统时确定NiosII结构支持以下寻址方式有:寄存器寻址:所打的操作数都是帘存器,结果保存在海存器屮移位寻址:寄存器和带符号的16位立即数相加的结災作为地址立即数寻址:操作数足指令屮的常姑寄存器间接寻址:使用丫移位寻址,以是移位值是常量0绝对寻址:范凼冇限制的绝对寻址使用带冇寄存器rO(它异常类型判别数裾,最高有效位在高地址。4GB扇地址空间32位宽度对此地址空间的读\n写将产生一个不确定的值的伉始终是0x00)的移位寻址來实现。指令集W对高速缓存实现初始化、Wj新及旁路数据高速缓存的指令操作。每个Avalon接口的PIO内核可提供32个I/O端口IL端口数可没置,用户可以添加一个或多个PIO内核。CPU通过I/O寄存器控制I/O端口的行为。I/O口可以配買为输入、输出和三态,还可以用來检测电平事件和边沿事件PIO内核提供了对硬件进行寄存器级访问的文件。SDRAM控制器内核概述:SDRAM控制器内核提供一个连接片外SDRAM芯片的Avalon接口,并可以同时连接多个SDRAM芯JioSDRAM控制器内核具不同数裾宽度(8、16、32或64位)、不同存容量和多八选择等设背。SDRAM控制器不支持禁能的时钟模式。SDRAM控制器使eke引脚永久地冇效。PPL(片内锁相环):通常用丁•调整SDRAM控制器内核-4SDRAM芯片之|川的相位差。Avalon三态桥:SDRAM控制器可与现喻三态桥共川引脚,这川能减少1/◦引脚使川,但将降低性能。fMAX(®高时钟频率):目标FPGA的系列和整个硬件设计都会影响硬件设计讨实现的S高时钟频率。Avalon主控制器川'以直接读Flash芯片。对于NiosII处理器用户,Altera捉供HAL系统库驱动程序和API函数來支持对Flash存储器的擦除和写操作。EI>CS控制器可用于:在EPCS器件中存储程序代码。存储非易失tt数据。管理FPGA配置数据。定时器是挂载在Avankm总线上的32位定时器,特性如下:两种计数模式:平次减丨和连续减1计数模式、定时器到达0时产生屮断请求(IRQ):讨选择设定为看门狗定时器,计算到达0时复位系统:讨选择输出周期性脉冲,在定时器计算到达()时输fli脉冲:可山软件启动、倥止或复位定时器;可山软件使能或屏蔽定时器中断。定时器可进行的基本操作如下所述:Avalon主控制器通过对控制寄存器执行不M的写操作來控制:•启动和停止定时器•使能/禁能IRQ•桁定单次减1计数或连续减1计数模式处现器读状态寄存器获取当前定吋器的运行信息。处理器可通过写数裾到periodl和periodh寄存器來设定定吋器周期。内部计数器计数减到0,立即从周期寄存器开始重新装载。处理器可以通过写snapl或snaph获取计数器的当前值。当计数器计数到达0时:•如果IRQ被使能,则产生一个IRQ•(可选的)脉冲发中器输出有效持续一个时钟周期•(可选的)看门狗输出K位系统实验一蜂鸣器和流水灯实验1、如何改变蜂鸣器呜叫的强度?通过改变延吋函数delay()屮的延吋吋间可及:现intmain(ait_u32N=1000000;alt_u32i=600000;"i;//喂狗