- 6.28 MB

- 2021-05-14 发布

- 1、本文档由用户上传,淘文库整理发布,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,请立即联系网站客服。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细阅读内容确认后进行付费下载。

- 网站客服QQ:403074932

PCB

结构、加工流程、线路阻抗控制

、

线路

阻抗

计算简介

1

Summary

2

PCB

结构

PCB

加工流程

PCB

线路阻抗控制

PCB

线路阻抗计算方法

PCB

结构

3

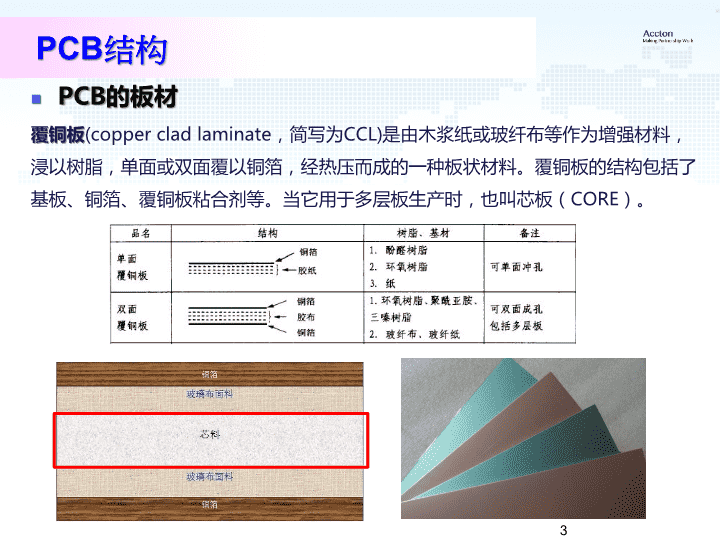

PCB

的板材

覆铜板

(copper clad laminate

,简写为

CCL)

是由木浆纸或玻纤布等

作

为

增强材料

,浸以树脂,单面或双面覆以铜箔,经热压而成的一

种

板状材料

。

覆铜板的结构包括了基板、铜箔、覆铜板粘合剂等。当它用于多层板生产时,也叫芯板(

CORE

)

。

4

覆铜板种类

一般

按基板的增强材料不同,可划分为:纸基、玻璃纤维布基、复合基

(CM

系列

)

、积层多

层板基和特殊材料基

(

陶瓷、金属芯基等

)

五大类。

常见的玻璃纤维布基

CCL

有环氧树脂

(FR-4

、

FR-5)

,它是目前最广泛使用的玻璃纤维布基

类型

。

备注:

一般

常规

FR-4

板料的

厚度

:

1

、

0.7mm

以下的板料是不含铜厚

的

;

2

、

0.7mm

及以上的又分为含铜和不含铜两种

。

比如

板厚

0.7mm

含

铜

,

就是

铜箔加芯板总厚度为

0.7mm

。

如果板厚

0.7mm

不含铜,在实际应用中板厚加上铜箔厚度就会超过

0.7mm

,

请注意此点区别。

最薄的芯板为

0.05mm

。

PCB

结构

5

铜箔的介绍

一般

按照铜箔不同的制法,可

分为

电解铜箔

(ED

)

和

压延

铜箔

(RA

)

两

大类

。

电解铜箔

(

Electrode Posited copper

)

是

通过专用电解机连续生产出的生箔再经表面处理而成。它是我们常用

硬板

PCB

的

铜箔材料。

压延铜箔

(Rolled Copper Foil)

是将铜板经过多次重复辊轧而制成的原箔

(

也叫毛箔

)

,根据要求进行粗化处理。由于压延铜箔耐折性和弹性系数大于电解铜箔,故适用于柔性覆铜箔

板

FPC

上

。

PCB

结构

电解铜箔的特点:

导电性好一些;分子比较疏松,易断;通过电镀工艺生产。

压延铜箔的特点:

绕曲性

较好;单价比电解铜箔贵;通过涂布工艺生产。

常用铜箔厚度类型:

1/4OZ

;

1/3OZ

;

1/2OZ

;

1OZ

;

2OZ

;

3OZ

6

半固化片

(PP)

半

固化片是一种片状材料,在一定温度和压力作用下,具有流动性并能迅速地固化和完成粘结过程,并与载体一起构成绝缘层,俗称半固化片或粘结片。因为英文名字叫

prepreg,

通常也叫

PP

。在实际压制完成后因内层残铜率及成品铜厚等因素的

影响

,

成品

厚度通常会比原始值小

10-15um

左右。

PCB

结构

7

半固化片

(PP)

为了满足阻抗要求,需要调整

PCB

叠层。

在实际生产中,同一个浸润层最多可以使用

3

张

半固化片

(

超过

3

张压合时,

PP

经高温由半固化状态转变成液态后容易从

Panel

板边

流失

)

,且最大厚度不能超过

20mil

。

超过此数据需要考虑增加芯板来制作,可以把芯板两面的铜箔蚀刻掉或者直接用光板,再在两面用半固化片粘连,这样可以实现较厚的浸润层。最少可以只用一个半固化片

,

但有的时候因内层铜箔分布稀疏,或者成品铜厚太厚

,

需要大面积填胶,厂家出于产品的可靠性考虑,

要求必须至少使用两张

PP

。

PCB

结构

PCB1

、

PCB2

使用的假八层叠层:

8

PCB

基材的常见

性能指标

TG

:

玻璃态转化温度,常规分为:

TG130-140

度

(常规),

TG150

度(中

TG)

,

TG170-175

度

(

高

TG)

。

介电常数

(DK)

:

它

是表示绝缘能力特性的一个系数。

FR4

通常在

3.9-4.6

之间

,

常见应用计算信号时延和特性阻抗:

信号时延计算公式:

特性阻抗计算公式:

损耗角正切值(

DF

)

:

也称损耗因子,是材料在交变力场作用下应变与应力周期相位差角的正切,也等于该材料的损耗模量与储能模量之比

;

通常损耗与

Dk&Df

关系密切,如下

为

介质

损耗

的近似计算

公式

:

热膨胀系数(

CTE)

:

高温时板子形变的性能指标

;

离子迁移(

CAF)

:

影响板子的

可靠性

;

漏电起痕指数(

CTI)

:

有关耐高压击穿的

参数

。

PCB

结构

9

PCB

基材的常见

性能指标

TU-862HF

Typical Dk/Df Value

:

TU-86PHF

Typical Dk/Df Value

:

PCB

结构

TU-862

板材

Datasheet

:

10

常见

板料供应

商

生

益、联茂、南亚、

台

耀

(

TU-862HF

)

、

台光、

ISOLA NECLO

、松下、日立、

ROGERS

、

ARLON

、

TACONIC

等

。

Rogers

:

RO4003

、

RO3003

、

RO4350(PTFE)

等

Tuc

:

862

、

872SLK

、

872SLK-SP

、

TU883

、

TU933

等

Panasonic

:

Megtron4/Megtron6

等

Isola

:

FR408HR/408

等

ShengYi

:

S1141/S1000-2

等

PCB

结构

11

PCB

加工流程介绍

内层

蚀刻

(DES

流程

)

:

显影

→

蚀刻

→

退膜

外层

蚀刻

(SES

流程

)

:

显影

→

镀铜

镀锡

→

退膜

→

蚀刻

→

退锡

为什么

PCB

内外层蚀刻方法不一样

?

内层

一般线宽线距较大,

故

有足够的孔环间距

;

外层

一般线路较密,空间不够,所以这个时候就需要想办法在不够的空间内达到做出线路的目的

。

碱性蚀刻

的

能力可以达到

1~2mil

的

孔环

,但是

酸性蚀刻

则

需要

5mil

左右,所以就必须使用锡将需要的线路先保护起来

。

内层蚀刻用干膜作为抗蚀层,而这种感光材料相对而言耐酸不耐碱的特性,故内层用酸性蚀刻。

PCB

加工流程

12

PCB

加工流程介绍

为什么

常规阻抗控制只能是

10%

的偏差?

1

、覆铜板来料

本身的偏差;

2

、

PCB

加工过程的蚀刻偏差;

3

、

PCB

加工过程中,层压带来的流胶率的偏差;

4

、高速

板材介质损耗,铜箔的表面粗糙度,

PP

的玻纤效应影响。

PCB

线路阻抗控制

13

1

、覆铜板来料本身的偏差

IPC-4101

《刚性及多层印制板用基材规范》

,

规定

覆铜板的尺寸公差要求包括长度、宽度、厚度、垂直度、弓曲和扭曲等几个公差要求。其中厚度及公差解释如下:

覆铜板的厚度偏差分为两种,一种厚度公差

包括

铜

箔

的厚度,另一种不包括铜箔的芯板厚度。

覆铜板(包括铜箔)厚度公差分三个等级(

K

、

L

和

M

),从

K

级至

M

级厚度偏差渐严。覆铜板(不包括铜箔)厚度偏差分四个等级(

A

、

B

、

C

、

D

),从

A

级至

D

级厚度偏差渐严。

D

级为用显微剖切法测得覆铜板上下金属箔之间的绝缘基板的最小距离。覆铜板(包括和不包括铜箔)厚度偏差见下表:

PCB

线路阻抗控制

14

2

、

PCB

加工过程的蚀刻偏差

线路

蚀刻

:

利用感光材料,将设计的线路图形通过曝光、显影、蚀刻的工艺步骤,达到所需铜面线路图形。

蚀刻

的目的:

蚀刻的目的是将图形转移以后有图形的受抗蚀剂保护的地方保留,其他未受保护的铜蚀刻掉,最终形成线路,达到导通的目的。

蚀刻分类:

蚀刻有酸性蚀刻和碱性蚀刻两种,通常内层采用酸性蚀刻,湿膜或干膜为抗蚀剂。外层采用碱性蚀刻,锡铅为抗蚀剂。

内层

蚀刻

(DES

流程

)

:显影

→

蚀刻

→

退膜

外层

蚀刻

(SES

流程

)

:显影

→

镀铜

镀锡

→

退膜

→

蚀刻

→

退锡

PCB

线路阻抗控制

内层蚀刻:

外

层蚀刻:

15

2

、

PCB

加工过程的蚀刻偏差

蚀刻

液在蚀刻过程中,不仅向下而且对左右各方向都产生蚀刻作用侧蚀是不可避免的。

蚀刻因子是指垂直蚀刻深度与横向侧蚀宽度

(

侧蚀量

)

两者之间的比值。侧蚀

是指导线每侧平行板面的最外缘

(

含抗蚀层

)

与导线内缩后的最内缘对比时两缘之空间距离

。

蚀刻

因子一般在

2~4

之间。线宽越小,蚀刻的精度公差越难控制。

蚀刻因子

=

蚀刻线厚

/[(

抗蚀层宽度

-

最窄线宽

)/2]

蚀刻过程的三种状态是:过度蚀刻、正常蚀刻和蚀刻不足。

PCB

线路阻抗控制

16

3

、

PCB

加工

过程中,层压

带来的流胶率的偏差

PCB

压合原理:

通过

“

热与压力

”

使

PP

结合不同内层芯板

和

外层铜箔

,

并利用外层铜箔作为外层线路之

基地。

半固化片的特性

:

1> RC

%

(

Resin content)

:

指

半固化片

中除了

玻纤布

以外

,树脂成分所占的重量百分比。

RC%

的多少直接影响到树脂填充导线间空隙的能力,同时决定压板后的介电层厚度。

2> RF

%

(

Resin flow

):

指压板后,流出板外的树脂占原来半固化片

总重

量

的

百分比。

RF%

是反映树脂流动性的指标,它也决定压板后的介电层厚度

3> VC

%

(

volatile content

):

指半固化片经过干燥后,失去的挥发成分的重量占

原来

半固化片总

重量

的百分比。

VC%

的多少直接影响压板后的品质。

PCB

线路阻抗控制

17

3

、

PCB

加工过程层压带来的流胶率的偏差

半固化片功能:

1>

作为

内外层线路的结合

介质

。

2>

提供

适当的绝缘层

厚度

。

半固化片

是

由玻纤布与树脂

组成

,

同

一种玻纤

布

PP

压

合后的厚度差别主要是由不同的树脂含量来调整而不是由压合条件来

决定

。

3>

阻抗控制

。

在主要四个影响因素中

,

Dk

值及介电层厚度两项是由

半固化片

片特性

来

决定

,

其

Dk

值可由

下列

公式

估算:

Dk=6.01-3.34RC%

RC%:

树脂含量

%

在

估算阻抗时所使用的

Dk

值

,可依据

胶片

RC%

作

推算。

PCB

线路阻抗控制

18

3

、

PCB

加工过程层压带来的流胶率的偏差

PP

填胶后的实际厚度计算如下:

PP

压合后

厚度

=

单张

PP

理论厚度

–

填胶损失

填胶损失

= (1-A

面内层铜箔残铜率

)x

内层铜箔厚度

+ (1-B

面内层铜箔残铜率

)x

内层铜箔厚度

内层

铜箔

残

铜率

=

內层走线面积

/

整板

面积

外层

的填胶损失

,只需

计算一面,不用计算外层的残铜率。

PCB

线路阻抗控制

19

4

、

高速板材介质损耗,铜箔的表面粗糙度,

PP

的玻纤

效应影响。

1>

介质损耗

介质损耗

与

Dk&Df

有直接

关系

,

Dk/Df

越稳定越好。

根据时延公式

1

可以知道,

Dk

越小传播时延也越小

(传播速度快,需要的时间就小),同时

Dk

的变化率越小阻抗也越稳定

,有利于阻抗的控制(公式

2

)。而从损耗公式(公式

3

)我们也可以知道

Dk/Df

越小(稳定),损耗也越小(稳定),

稳定的材料参数可以在工程应用上更好的控制产品的性能。

PCB

线路阻抗控制

公式

1

,信号时延:

公式

2

,特性阻抗:

公式

3

,介质损耗:

20

4

、

高速板材介质损耗,铜箔的表面粗糙度,

PP

的玻纤

效应影响。

2>

铜箔表面粗糙度

左

图是

几种常规的铜箔对表面粗糙度的定义,其中有

STD(

标准铜箔

)

、

RTF(

反转铜箔

)

和

VLP/HVLP(

低

/

超低表面粗糙度铜箔

)

,可见不同的铜箔铜牙

(

粗糙度

)

相差明显

。

右

图

是

普通

铜箔与低表面粗糙度铜箔的切片放大图

。

从图中可以直接看出铜箔粗糙度

(

铜牙

)

使线路的宽度、线间距不均匀,从而影响阻抗的不可控,最后导致一系列的高速信号完整性问题,而低表面粗糙度的铜箔就不会导致类似问题。

PCB

线路阻抗控制

21

4

、

高速板材介质损耗,铜箔的表面粗糙度,

PP

的玻纤

效应影响。

3> PP

的玻纤效应

目前

主流的材料都是采用的“

E-glass”

,

参照

的

IPC-4412A

规范

,常见

玻纤的微观放大如下

图

所示:

从

上

图可知

不同的玻纤对应的编织粗细不一样,开窗和交织的厚度也

不一样

。

信号分别在

开窗上和玻纤上所表现的特性

(

阻抗、时延、损耗

)

也不一样(开窗和玻纤

Dk/Df

特性不一样导致的),这就是

玻纤效应

。

在高速信号的设计上应该尽量避免玻纤效应的影响,常用的方法是采用一定角度走

线

,

或者

在

制板的时候让

板厂

旋转一定的角度

(

板材的利用率会有一定的下降

)

,

或者

直接采用开窗比较小的开纤布

或者平

织布,此外用

2

层

PP

也可以适当的避免玻纤效应。

PCB

线路阻抗控制

22

PCB1

、

PCB2

叠层信息

PCB

线路

阻抗计算方法

23

微带线介绍

对于

信号线而言,在板子上实现的形式又分为

微带线

和

带状线

,两者的不同,使得阻抗计算选择的结构不

一致

。

微带线

:

微带线的特点就是只有一个参考层,上面盖绿油。下面是

单

端

线

(

50

Ω)和差分线(

100

Ω)的具体参数

设置

(

参考

PCB1

、

PCB2 L1

、

L6

叠层阻抗

)

。

PCB

线路

阻抗计算方法

24

微带线阻抗计算说明

1

、

H1

是表层到参考层的介质厚度,不包括参考层的铜厚;

2

、

C1

、

C2

、

C3

是绿油的

厚度,

其厚度对于阻抗有细微影响,这也是处理文字面时,尽量不让丝印放置在阻抗线上的原因;

3

、

T1

是

表层

铜厚加电镀的厚度,

1.91mil

为

1/3oz Copper Foil + Plating

的结果;

4

、一般

W1

是板上走线的宽度,由于加工后的线为梯形,所以

W2